Contents

1. 능동 저역 통과 필터란?

능동 저역 통과 필터는 오퍼레이션 앰프(op-amp)와 저항, 커패시터 등의 부품을 사용하여 낮은 주파수에서 필터와 비슷한 작동을 하는 필터 회로입니다.

기본적인 1차 수동 필터 회로는 단일 저항과 비편광 커패시터를 사용하여 낮은 주파수에서 신호를 걸러내는 저역 통과 필터나 고주파에서 신호를 걸러내는 고역 통과 필터를 만들 수 있습니다.

하지만 패시브 필터의 단점은 출력 신호의 크기가 입력 신호보다 작아지는 것입니다.

수동 필터 회로가 복수의 단계로 이루어진 경우, 이 신호 크기 감소를 “감쇠”라고 부릅니다.

이 신호 감쇠를 제어하거나 복원하는 한 가지 방법은 능동 필터를 사용하여 신호를 증폭하는 것입니다.

능동 필터는 회로 설계 내에 오퍼레이션 앰프, 트랜지스터 또는 FET와 같은 능동 부품이 들어 있습니다.

이들은 외부 전원 공급에서 전력을 공급받아 출력 신호를 증폭하거나 조절합니다.

필터 증폭은 또한 필터의 주파수 응답을 조절하거나 형성하는 데 사용됩니다.

출력 응답을 더 선택적으로 만들어 필터의 출력 대역폭을 조절할 수 있습니다.

따라서 “수동 필터”와 “능동 필터”의 주요 차이는 신호 증폭에 있습니다.

능동 필터는 일반적으로 오퍼레이션 앰프를 사용하여 설계됩니다.

이 때문에 오퍼레이션 앰프는 높은 입력 임피던스, 낮은 출력 임피던스, 그리고 피드백 루프 내의 저항 네트워크에 의해 결정되는 전압 이득을 갖습니다.

패시브 고역 통과 필터가 이론적으로 무한한 고주파 응답을 갖는 것과 달리, 능동 필터의 최대 주파수 응답은 사용되는 오퍼레이션 앰프의 이득/대역폭 곱(또는 오픈 루프 이득)으로 제한됩니다.

그럼에도 불구하고, 능동 필터는 일반적으로 패시브 필터보다 디자인하기 쉽고, 좋은 성능 특성, 뛰어난 정확도, 급격한 롤오프 및 낮은 소음을 제공합니다.

- 연관 참조 : RC 수동 저역 통과 필터,출력 전압 계산,예제2,주파수 응답,2차 LPF 주파수 응답

- 연관 참조 : RL 수동 저역 통과 필터, LPF 종류,동작 원리,상한 차단 주파수, 예제1

- 연관 참조 : 수동 RC 고역 통과 필터,Ideal,Real,주파수 응답,출력 전압 및 게인,예제1, 2차필터

- 연관 참조 : 수동 대역 통과 필터란?, RLC을 사용한 BPF회로,주파수 응답, 예제1,요약

- 연관 참조 : 능동 고역 통과 필터,이상적인 HPF, 전압 이득, 주파수 응답

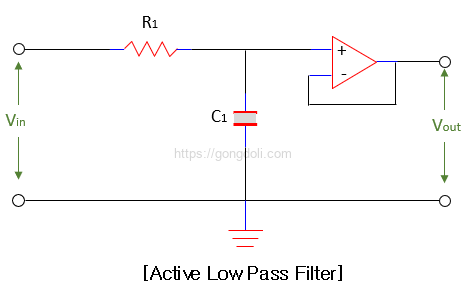

2. 1차 능동 저역 통과 필터

능동 저역 통과 필터는 낮은 주파수의 신호를 통과시키고 고주파 신호를 차단하는 회로입니다.

이 필터는 오퍼레이션 앰프와 저항, 커패시터 등의 부품을 사용하여 구성됩니다.

1차 저역 통과 필터의 가장 간단한 형태는 인버팅 증폭기와 기본 RC 저역 통과 필터 회로를 결합하는 것입니다.

이를 통해 저역 통과 필터의 특성을 얻을 수 있습니다.

오퍼레이션 앰프는 전기 회로에서 매우 중요한 부품 중 하나입니다.

이 회로에서는 앰프를 “비인버팅 모드”로 구성합니다.

이는 입력 신호가 앰프의 입력으로 들어가고 출력은 입력과 같은 방향으로 증폭된다는 것을 의미합니다.

이렇게 함으로써 앰프는 입력 신호를 증폭하지만, 입력과 출력 간의 전압은 동일하게 유지됩니다.

그 결과로 이 필터는 저역 통과 특성을 유지하면서 입력 신호를 증폭시킵니다.

이 구성은 이전에 본 패시브 RC 필터와 다르게, DC 이득이 1인 전압 팔로워 구성을 가지고 있습니다.

이것은 입력과 출력 사이의 전압이 변하지 않음을 의미합니다.

이 구성의 주요 장점은 오퍼레이션 앰프의 높은 입력 임피던스로 인해 필터의 출력에 부하가 걸리지 않는다는 것입니다.

또한 낮은 출력 임피던스로 인해 부하 임피던스의 변화가 필터의 차단 주파수에 영향을 주지 않습니다.

그러나 이 구성의 단점은 출력의 전압 이득이 1보다 크지 않다는 것입니다.

이는 입력과 출력의 전압이 동일하다는 것을 의미하며, 따라서 실제로 입력 신호를 증폭하지 않습니다.

이러한 제약을 극복하려면 더 높은 전압 이득이 필요한 경우 다른 회로 구성을 고려해야 합니다.

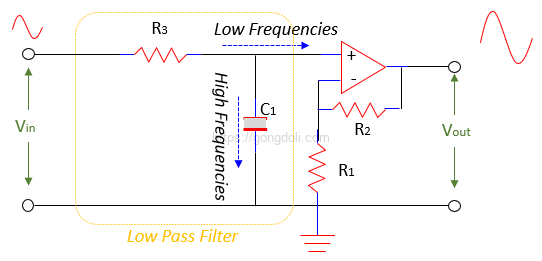

3. 증폭 기능이 있는 능동 저역 통과 필터

능동 저역 통과 필터는 일반적으로 입력 신호를 증폭하는 기능도 수행할 수 있습니다.

이를 위해서는 이전에 설명한 저역 통과 필터 회로에 약간의 수정을 가할 필요가 있습니다.

3-1) 1차 능동 저역 통과 필터 회로

가장 간단한 방법은 비인버팅 증폭기를 사용하여 출력 신호를 증폭하는 것입니다.

비인버팅 증폭기는 입력과 출력 간의 전압을 증폭하지만, 입력 신호와 출력 신호는 동일한 방향으로 유지됩니다.

이를 위해서는 이전의 저역 통과 필터 회로 뒤에 비인버팅 증폭기를 추가하면 됩니다.

3-2) 1차 능동 저역 통과 필터 DC 이득

출력의 진폭은 증폭기의 통과대역 이득(AF)에 의해 증가됩니다.

비인버팅 증폭기 회로의 경우, 필터의 전압 이득은 피드백 저항(R2)을 해당 입력 저항(R1)으로 나눈 값으로 주어집니다.

비인버팅 증폭기의 DC 이득은

DC 이득=1+(R2/R1)

- 여기서

- R1은 입력 저항

- R2는 피드백 저항

이러한 이득은 증폭기의 특성에 따라 입력 신호가 DC (직류) 성분을 포함할 때 적용됩니다.

일반적으로 비인버팅 증폭기의 DC 이득은 1 이상이며, R2가 R1보다 큰 경우에는 추가 증폭이 발생합니다.

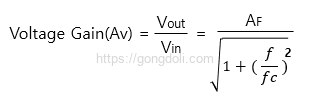

3-3) 1차 능동 저역 통과 필터 전압 이득

1차 저역 통과 필터의 전압 이득은 주파수(f), 차단 주파수(fc), 그리고 통과대역 이득(AF)의 함수로 표현될 수 있습니다.

여기서:

- AF는 필터의 통과대역 이득으로, 1+R2/R1

- f는 입력 신호의 주파수(Hz)

- fc는 차단 주파수(Hz)

이 공식은 주파수의 함수로 필터의 전압 이득을 나타냅니다.

입력 신호의 주파수가 변할 때, 필터의 이득도 그에 따라 변화합니다.

차단 주파수보다 훨씬 낮은 주파수에서는 이득이 통과대역 이득(AF)에 접근합니다.

주파수가 차단 주파수를 향해 다가가면, 이득은 감소하여 입력 신호의 고주파 구성 요소를 감쇠합니다.

따라서, 저역 통과 능동 필터의 작동은 위의 주파수 이득 공식에서 다음과 같이 확인할 수 있습니다

3-3-1) 매우 낮은 주파수에서 (f<fc)일 때

- 저역 통과 필터는 매우 낮은 주파수에서 입력 신호를 거의 전부 통과시킵니다.

- 이때, 필터의 이득은 주파수에 따라 거의 변하지 않고, 통과대역 이득인 AF=Vout/Vin에 가깝게 유지됩니다.

- 따라서, 저주파에서는 필터의 작동이 주로 입력 신호를 증폭하는 데 있습니다.

3-3-2) 차단 주파수에서 (f=fc)일 때

- 저역 통과 필터의 차단 주파수에서는 입력 신호의 주파수가 차단 주파수와 같아집니다.

- 이때, 필터의 이득은 통과대역 이득의 절반, 즉 AF/√2=0.707AF가 됩니다.

- 이는 입력 신호의 저주파 구성 요소는 여전히 증폭되지만, 고주파 구성 요소는 차단되어 감쇠됩니다.

3-3-3) 매우 높은 주파수에서 (f>fc)일 때

- 고주파에서는 필터의 이득이 점차적으로 감소하게 됩니다.

- 입력 신호의 주파수가 차단 주파수보다 높아질수록 필터는 고주파 구성 요소를 더 많이 차단하게 되어, 출력 신호의 진폭이 줄어들게 됩니다.

이러한 각각의 상황에서, 저역 통과 필터의 동작을 이해하고 주파수에 따른 이득의 변화를 파악할 수 있습니다.

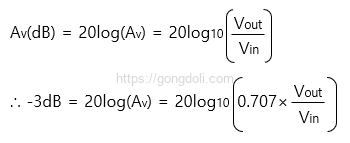

3-4) 전압 이득(dB)

전압 이득의 크기를 데시벨(dB)로 표현하는 이유는 데시벨 스케일을 사용하면 신호의 크기를 더 직관적으로 이해할 수 있기 때문입니다. 일반적으로 전압 이득이 크면 데시벨 값도 더 커지며, 전압 이득이 작으면 데시벨 값도 작아집니다.

데시벨로 전압 이득을 계산하기 위해서는 먼저 주어진 전압 이득 값을 로그함수의 입력으로 사용하여 그 값을 10을 밑으로 하는 로그를 취해야 합니다. 이후에 20을 곱하여 데시벨 값으로 변환합니다.

수식으로 표현하면 다음과 같습니다:

여기서 Av는 주파수에 따른 전압 이득을 나타냅니다.

이를 통해 각 주파수에서의 전압 이득을 데시벨로 변환할 수 있습니다.

이를 통해 필터의 주파수 응답을 더 직관적으로 이해할 수 있습니다.

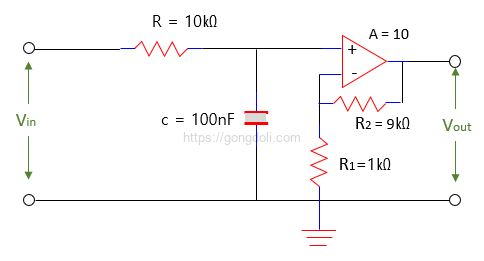

4. 능동 저역 통과 필터 예제

저주파에서 이득이 10인 비인버팅 능동 저역 통과 필터 회로를 설계하고, 고주파 차단 또는 코너 주파수가 159Hz이며 입력 임피던스가 10KΩ인 회로를 설계해보겠습니다.

주어진 사양에 맞는 전압 이득이 10인 비인버팅 능동 저역 통과 필터 회로를 설계하기 위해서는 다음 단계를 따를 수 있습니다.

- 저주파에서 원하는 이득을 얻기 위한 저항 R1과 R2의 값을 결정합니다.

- 차단 주파수(fc)를 설정하기 위해 캐패시터 C의 값을 계산합니다.

- 회로의 입력 임피던스가 요구 사항을 충족하는지 확인합니다.

먼저 첫 번째 단계부터 시작해보겠습니다.

- 이득 계산 : 비인버팅 증폭기의 전압 이득(Av)은 다음과 같은 공식으로 주어집니다.

Av =1+(R2/R1)

저주파에서 원하는 이득이 10인 경우(Av=10), R1=1kΩ로 선택하고 R2를 구합니다.

10 =1+(R2/1KΩ)

R2=9kΩ - 차단 주파수 계산 : 1차 저역 통과 필터의 차단 주파수(fc)는 다음과 같은 공식으로 주어집니다.

fc=1/(2πRC)

주어진 차단 주파수가 159Hz인 경우, R=10kΩ로 선택하고 C를 구합니다.

159=1/(2π×10kΩ×C)

C≈100nF - 입력 임피던스 : 비인버팅 증폭기 구성의 입력 임피던스는 다음과 같이 주어집니다.

Zin=R1

여기서 R1=1kΩ이므로 요구 사항을 충족합니다.

이러한 계산에 따라 비인버팅 능동 저역 통과 필터 회로는 다음과 같이 설계됩니다

- R1=1kΩ

- R2=9kΩ

- C≈100nF

이 회로는 저주파에서 전압 이득이 10이 되며, 차단 주파수가 159Hz이며, 입력 임피던스가 10kΩ인 비인버팅 능동 저역 통과 필터를 갖게 됩니다.

It?¦s actually a great and useful piece of info. I am satisfied that you shared this helpful info with us. Please keep us informed like this. Thanks for sharing.

Thank you for your kind words! I’m so glad you found the information helpful. I’ll keep sharing more updates.

I’ve been surfing on-line greater than 3 hours lately, yet I never found any interesting article like yours. It is lovely price enough for me. Personally, if all webmasters and bloggers made just right content material as you probably did, the internet will be much more helpful than ever before. “Where facts are few, experts are many.” by Donald R. Gannon.

Thank you so much for your thoughtful and encouraging feedback! It’s truly heartening to hear that you found the content both engaging and valuable.

Hey there! I’m at work surfing around your blog from my new apple iphone! Just wanted to say I love reading your blog and look forward to all your posts! Carry on the fantastic work!

Thank you so much for the kind words!

I’m so glad you’re enjoying the blog, and I’ll definitely keep the posts coming

Thanks a lot for providing individuals with remarkably pleasant opportunity to read from this blog. It is usually so terrific and as well , full of fun for me personally and my office peers to visit your web site at the least thrice every week to see the newest issues you have got. Of course, I am also at all times pleased concerning the mind-blowing things you serve. Some 3 facts in this posting are truly the most suitable I have had.

I’m truly grateful for your thoughtful message—it means a lot to know that the blog brings joy and value to you and your colleagues.

Hearing that you visit regularly and find the content both fun and insightful is incredibly rewarding.

I’ll keep doing my best to share meaningful ideas, and I’m thrilled that this post stood out to you.

Thank you again for your kind support!

An impressive share, I just given this onto a colleague who was doing a little analysis on this. And he in fact bought me breakfast because I found it for him.. smile. So let me reword that: Thnx for the treat! But yeah Thnkx for spending the time to discuss this, I feel strongly about it and love reading more on this topic. If possible, as you become expertise, would you mind updating your blog with more details? It is highly helpful for me. Big thumb up for this blog post!

That’s such a fun and thoughtful message—thank you!

I’m glad the post was helpful enough to earn you breakfast (now that’s a win!).

I always was interested in this subject and stock still am, regards for posting.

Glad it resonated with you—thanks for reading!

Hey There. I discovered your blog the usage of msn. That is an extremely neatly written article. I will make sure to bookmark it and return to read more of your helpful info. Thanks for the post. I’ll certainly comeback.

I truly appreciate your kind words, and I’m glad you plan to return for more.

You have noted very interesting points! ps decent site. “It is better to be hated for who you are than to be loved for what you are not.” by Andre Gide.

I truly appreciate your kind words

Great line up. We will be linking to this great article on our site. Keep up the good writing.

Thank you! I appreciate your support and I’m glad you’ll be sharing the article.

What i do not understood is if truth be told how you are now not actually much more neatly-liked than you might be right now. You’re so intelligent. You know therefore considerably relating to this subject, made me personally consider it from so many numerous angles. Its like women and men are not fascinated except it’s one thing to accomplish with Lady gaga! Your own stuffs outstanding. Always maintain it up!

Thank you so much for your generous words. I’m glad the post gave you new perspectives, and I truly appreciate your encouragement.

Hi there, I found your web site via Google while looking for a related topic, your site came up, it looks good. I have bookmarked it in my google bookmarks.

Thank you for visiting and bookmarking my site.

Hey there, You’ve done an excellent job. I’ll definitely digg it and personally recommend to my friends. I’m confident they will be benefited from this site.

Thank you for your generous support. I’m glad you find the site helpful.

You could definitely see your skills in the paintings you write. The world hopes for even more passionate writers like you who aren’t afraid to mention how they believe. At all times go after your heart.

I do agree with all of the concepts you’ve offered on your post. They are very convincing and can certainly work. Nonetheless, the posts are too short for newbies. May you please prolong them a bit from subsequent time? Thank you for the post.

Thank you for your feedback! I’ll keep in mind to make future posts more detailed for beginners.