Contents

1. 디커플링 커패시터란 무엇인가?

회로를 설계하다 보면 빠지지 않고 등장하는 부품이 있습니다. 바로 디커플링 커패시터(Decoupling Capacitor)입니다.

초보자 분들에겐 다소 생소하게 느껴질 수 있지만, 이 커패시터는 고속 디지털 회로나 아날로그 회로에서 전원 품질을 안정적으로 유지하는 데 필수적인 부품입니다.

그렇다면, 디커플링 커패시터는 정확히 무엇이며, 왜 필요한 걸까요?

디커플링 커패시터의 가장 큰 역할은 전원 노이즈(Noise)를 제거하거나 억제하는 것입니다.

IC나 마이크로컨트롤러가 동작할 때, 내부 회로에서는 아주 빠른 속도로 전류를 끌어다 씁니다.

이때 순간적인 전류의 변화가 전원선에 노이즈로 나타나고, 인접한 다른 회로나 IC에도 영향을 주게 됩니다.

이런 문제를 해결하기 위해 전원과 GND 사이에 커패시터를 달아주는 것, 이것이 바로 디커플링 커패시터의 기본 동작 방식입니다.

쉽게 말해, 전원과 IC 사이에 ‘충격 흡수기’를 하나 달아주는 것이라고 생각하면 됩니다.

즉, 전류가 급하게 필요할 때 디커플링 커패시터가 먼저 응답해서 빠르게 전류를 공급해주고, 전원 노이즈가 회로 전체로 퍼지는 걸 막아줍니다.

전원선은 단순한 ‘전압 공급선’이 아니라, 사실상 하나의 고속 전송선로처럼 작동합니다.

이 선로에는 임피던스, ESL(등가 직렬 인덕턴스), ESR(등가 직렬 저항)이 존재하고, 고속 전류가 흐를수록 이 값들이 문제를 일으킬 수 있습니다.

- ESL (Equivalent Series Inductance): 주파수가 높아질수록 커패시터가 인덕터처럼 작동하게 되어, 원하는 고주파 노이즈를 제거하지 못하게 됩니다.

- ESR (Equivalent Series Resistance): 커패시터 내부의 저항성 요소로, 노이즈 제거 능력이나 발열에 영향을 줍니다.

이 때문에 디커플링 커패시터는 단순히 하나만 사용하는 게 아니라, 여러 개를 병렬로 구성하거나 0.1μF, 1μF, 10μF 같은 다양한 용량의 커패시터를 함께 사용하는 방식으로 설계하는 것이 일반적입니다.

이렇게 하면 각 주파수 대역에 걸쳐 노이즈 제거 효과를 극대화할 수 있습니다.

- 연관 참조 : 전송선로에서 Crosstalk 저감 설계,부하 조건에 따른 반사,종단 방식 4가지 특성

- 연관 참조 : 고속 PCB 신호 간섭,NEXT와 FEXT, Crosstalk 저감 설계,단일종단 vs 차동신호

- 연관 참조 : 차동신호의 원리와 차동 PCB 설계,주요 특징,라인 설계,3-도체 시스템

- 연관 참조 : 노이즈 필터 종류와 원리,Common Mode Choke,전원라인 필터,3단자 Cap

- 연관 참조 : 방사 노이즈 원인, DM과 CM전류,디지털 방사, 노이즈 대책 6가지와 종류

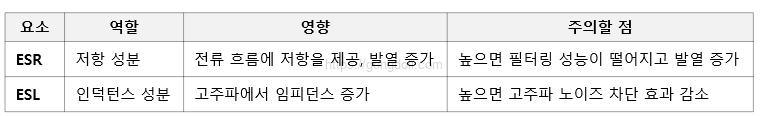

2. ESR과 ESL 이해하기

디커플링 커패시터(Decoupling Capacitor)는 전원 공급 장치에서 발생할 수 있는 고주파 노이즈를 필터링하고, 빠르게 변화하는 전압 요구 사항을 충족시키는 중요한 부품입니다.

하지만 단순히 커패시터의 용량만 보고 설계할 경우, 성능이 기대에 미치지 않을 수 있습니다.

커패시터 내부의 ESR(등가 직렬 저항)과 ESL(등가 직렬 인덕턴스)은 신호의 품질과 회로의 성능에 중요한 영향을 미칩니다.

2-1) Equivalent Series Resistance (ESR)의 의미

ESR(Equivalent Series Resistance)은 커패시터의 내부 저항입니다.

실제로 모든 커패시터는 이상적인 커패시터가 아니라, 전극과 내부 리드선 등에서 저항을 가집니다.

이 ESR은 커패시터의 주파수 응답, 즉 얼마나 잘 필터링할 수 있는지에 중요한 영향을 미칩니다.

- ESR이 낮으면 → 전류 흐름에 저항이 적어져 필터링 성능이 높아짐

- ESR이 높으면 → 필터링 성능 저하, 발열 증가

따라서 디커플링 커패시터를 사용할 때 ESR이 낮은 제품을 선택하는 것이 고속 회로에서 중요한 이유입니다.

2-2) Equivalent Series Inductance (ESL)의 영향

ESL(Equivalent Series Inductance)은 커패시터가 내부 구조나 리드선으로 인해 나타내는 인덕턴스 성분입니다.

ESL은 주로 고주파에서 중요한 요소로, 커패시터가 고주파 신호를 얼마나 잘 처리할 수 있는지에 영향을 미칩니다.

- ESL이 크면 → 고주파 신호를 차단하고 임피던스가 급격히 증가

- ESL이 작으면 → 고주파 신호를 잘 통과시켜, 고주파 노이즈 필터링에 유리

직관적으로 이해하면, ESL은 커패시터의 리드선 길이나 구조에 의한 ‘꼬임’ 같은 것이라고 생각할 수 있습니다.

2-3) ESR/ESL이 회로 성능에 미치는 영향

디커플링 커패시터는 ESR과 ESL 값에 따라 회로의 성능에 큰 영향을 미칩니다.

고주파 신호에서의 성능을 최적화하려면 ESL이 낮아야 하며, 저주파에서의 성능을 최적화하려면 커패시턴스(C)가 커져야 합니다.

2-4) MLCC와 ESR/ESL 특성

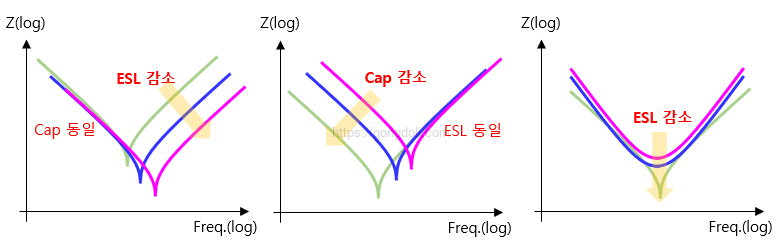

디커플링 커패시터로 주로 사용되는 커패시터는 MLCC(다층 세라믹 커패시터)입니다.

MLCC는 낮은 ESR과 ESL을 가질 수 있어 고속 회로에서 매우 유리합니다.

MLCC의 특성에 따라 ESL이 작아질수록 고주파에서의 자체 공진 주파수(SRF)가 더 높은 주파수로 이동합니다.

또한 커패시턴스(C) 값이 커지면 저주파에서의 임피던스가 낮아지며, ESR 값이 변화하면 공진 주파수 영역에서 임피던스 값의 변화가 발생합니다.

- ESL이 작아질수록 → 고주파 영역에서 특성이 좋아짐

- 커패시턴스 값이 커질수록 → 저역에서 임피던스 감소

- ESR이 바뀌면 → 주로 공진 주파수에서 임피던스 변동

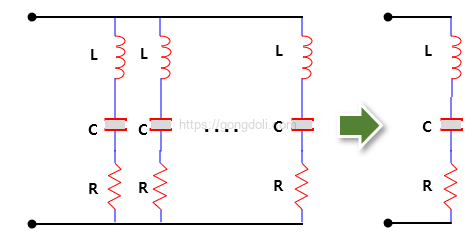

2-5) 커패시터 병렬 연결의 효과

커패시터를 병렬로 연결하면 ESL과 ESR을 줄이는 효과가 있습니다.

예를 들어, 동일한 커패시터를 여러 개 병렬로 연결하면 각 커패시터의 커패시턴스(C) 값은 n배 증가하고, ESL과 ESR은 1/n배로 감소합니다.

이는 병렬 연결을 통해 커패시턴스 값을 증가시키고 고주파에서의 성능을 향상시킬 수 있음을 의미합니다.

- 커패시턴스(C) 값은 n배 증가

- ESL과 ESR은 1/n배로 감소

또한 커패시터를 대용량부터 소용량까지 병렬로 구성하면, 넓은 주파수 대역에서 임피던스를 효과적으로 낮출 수 있습니다.

대용량 커패시터는 저주파에서 임피던스를 낮추고, 소용량 커패시터는 고주파에서 임피던스를 낮추는 특성을 가집니다.

이러한 특성을 이용해 다양한 크기의 커패시터를 병렬로 연결하면, 넓은 주파수 대역에서 전원선로 임피던스를 낮출 수 있습니다.

디커플링 커패시터는 회로에서 매우 중요한 역할을 합니다.

ESR과 ESL 값이 낮은 커패시터를 사용하면 고속 회로에서 노이즈를 효과적으로 제거하고, 신호의 정확성을 유지할 수 있습니다.

특히 MLCC 커패시터는 낮은 ESR과 ESL을 가짐으로써 고주파에서 뛰어난 성능을 발휘합니다.

또한 커패시터를 병렬로 연결하는 방식으로 임피던스 저감을 더욱 효율적으로 할 수 있습니다.

디커플링 커패시터 선택 시 ESR과 ESL을 고려하여 적절한 용량을 선택하고, 병렬 연결을 통해 주파수 대역에 맞는 임피던스 특성을 확보하는 것이 중요합니다.

3. PCB 패턴 커패시터(Pattern Cap)의 구조와 특성

회로 설계에서 디커플링 커패시터는 빠질 수 없는 핵심 부품입니다.

노이즈 억제, 전압 안정화, 고속 동작 회로의 안정성 확보 등 수많은 역할을 합니다.

그런데 디커플링 커패시터를 꼭 MLCC 같은 칩 부품으로만 써야 할까요?

답은 “아니오”입니다.

PCB 자체도 훌륭한 디커플링 커패시터가 될 수 있습니다.

바로 패턴 커패시터(Pattern Capacitor) 혹은 면 커패시터(Plane Capacitor)라고 부르는 방식입니다.

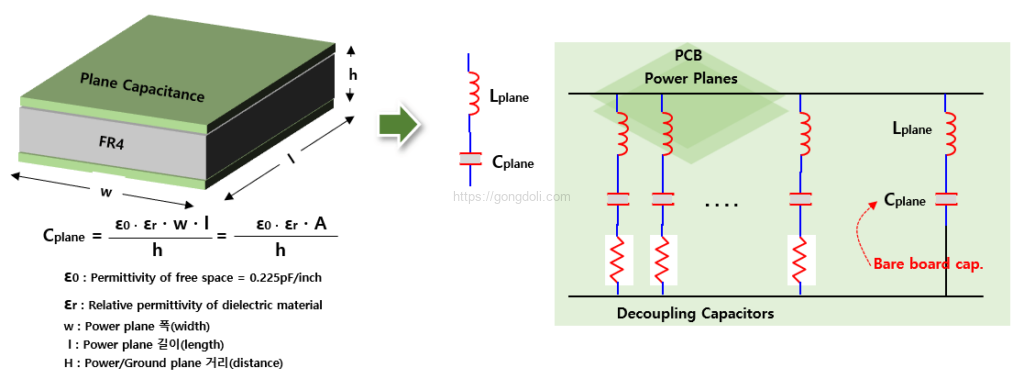

3-1) 실장면에서의 동작 원리

그런데 PCB를 생각해보시기 바랍니다.

Power(전원층)과 GND(접지층)이 넓은 면적으로 배치되고, 그 사이에 FR4 같은 유전체가 들어가 있습니다.

이건 구조적으로 일반 커패시터와 다를 바가 없습니다.

즉, PCB의 전원층과 접지층 사이도 충분히 커패시터처럼 동작할 수 있다는 것입니다.

이런 구조를 이용한 디커플링 구조를 패턴 커패시터, 또는 베어 보드 커패시터(Bare Board Capacitor)라고 부릅니다

물론 그냥 단순히 패턴만 있다고 커패시터처럼 잘 동작하진 않습니다.

면적은 넓고, 두께는 얇고, 유전율은 높은 구조여야 의미 있는 커패시턴스를 얻을 수 있습니다.

위에 공식에서 보듯, 면적이 넓을수록, 두께가 얇을수록 커패시턴스는 커집니다.

그래서 고속 회로에서는 아주 얇은 prepreg를 쓰기도 합니다.

3-2) 일반 커패시터와의 차이

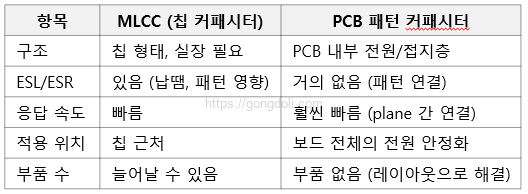

그렇다면, 우리가 평소에 쓰던 MLCC와 이런 패턴 커패시터는 뭐가 다를까요?

특히 중요한 차이점은 ESL입니다.

MLCC 같은 부품 커패시터는 납땜, 패턴, 비아 등을 통해 연결되기 때문에 아무리 작은 패키지를 써도 ESL이 생깁니다.

하지만 PCB 패턴 커패시터는 VCC와 GND plane이 바로 붙어 있으니 ESL이 거의 없다시피 합니다.

그래서 고속 응답이 필요한 영역에서는 이 방식이 훨씬 유리하게 됩니다.

디커플링 커패시터 중 MLCC는 저역(수 MHz ~ 수십 MHz)에서 효과적으로 임피던스를 낮춰줍니다.

반면에 PCB 자체에 내장된 면 커패시터는 수백 MHz 이상의 고역에서 탁월한 임피던스 저감 효과를 보입니다.

이유는 간단합니다.

ESL(기생 인덕턴스)와 ESR(기생 저항)이 거의 없기 때문입니다.

MLCC는 아무리 소형 패키지를 써도 리드, 납땜, 패턴 등의 영향으로 ESL이 존재합니다.

하지만 PCB 패턴 커패시터는 전원층과 접지층이 바로 붙어 있기 때문에 ESL이 거의 제로에 가깝습니다.

덕분에 고속 회로나 고주파 영역에서 전원 안정화에 매우 효과적입니다.

3-3) 패턴 커패시터를 설계할 때 고려할 점

위에 커패시턴스 공식에서 보듯, PCB의 커패시턴스를 늘리려면 다음 3가지를 고려해야 합니다.

- 면적(A)을 넓힌다 – 가능한 넓게 전원/접지 plane을 구성합니다.

- 두께(d)를 얇게 한다 – 전원과 접지층 사이의 prepreg 두께를 줄입니다.

- 유전율(ε)을 높인다 – FR4보다 유전율이 높은 재료 사용 (예: 고속 PCB 재료)

실제로 고속 설계에서는 0.05mm에서 0.075mm 이하의 매우 얇은 절연층을 적용하여 수 nF 단위의 커패시턴스를 확보합니다.

물론 MLCC처럼 수십~수백 nF 이상의 큰 용량은 아니지만, 수백 MHz 이상의 고주파 대역에서는 이 정도 커패시턴스만으로도 충분한 디커플링 효과를 얻을 수 있습니다.

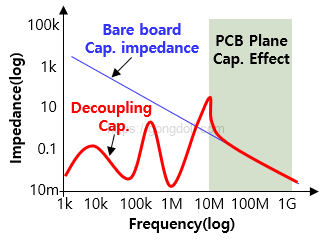

4. 다중 병렬 커패시터 특성

고속 회로나 디지털 회로를 설계해본 경험이 있다면, 아마도 한두 개의 디커플링 커패시터로는 전원 품질이 충분히 확보되지 않는다는 걸 느끼셨을 겁니다.

그래서 많은 설계자들이 ‘다중 병렬 디커플링 커패시터’를 전략적으로 사용하곤 합니다.

그런데 단순히 “여러 개 달면 좋다”가 아니라, 그 안에는 나름의 물리적인 원리와 전기적인 이유가 존재합니다.

디지털 회로나 고속 회로에서는 회로 동작 중 수 ns 단위로 전류가 확 튀는 경우가 많습니다.

이런 급격한 전류 변화는 전원 선로에 잡음을 만들고, 때로는 IC 동작 오류까지 유발할 수 있습니다.

그래서 이때 빠르게 전류를 공급해주는 “근처 배터리 역할”을 하는 게 바로 디커플링 커패시터입니다.

말 그대로, 디지털 칩에서 요구하는 순간적인 전류를 대신 흡수하거나 공급해주는 장치라고 생각할 수 있습니다.

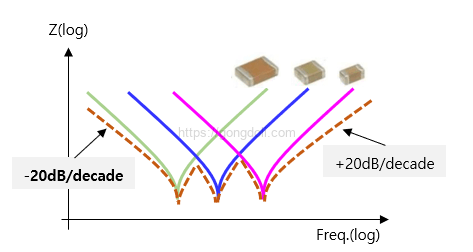

사실 커패시터는 이론적으로는 그냥 전류를 저장하는 수동 소자지만, 실제로는 인덕턴스(ESL, Equivalent Series Inductance) 성분이 함께 존재합니다.

이 ESL 때문에 커패시터는 단순히 일정 주파수까지 동작하고, 그 이후부터는 오히려 인덕터처럼 행동합니다.

- 자체 공진 주파수(f₀): 커패시턴스(C)와 ESL(L) 사이에서 공진이 일어나는 주파수

- f₀ 이하에서는 → 커패시터처럼 동작 (임피던스 ↓)

- f₀ 이상에서는 → 인덕터처럼 동작 (임피던스 ↑)

그래서 임피던스 그래프는 “V”자 형태를 그립니다.

이걸 잘 이해하면 왜 여러 개의 디커플링 커패시터를 병렬로 사용하는지 감이 옵니다.

만약 서로 다른 커패시터를 병렬로 쓸 때 무슨 일이 일어날까?

이제부터 진짜 재미있는 부분입니다.

예를 들어 큰 용량(10μF)에 ESL이 큰 커패시터 C1과, 작은 용량(0.1μF)에 ESL이 작은 커패시터 C2를 병렬로 연결했다고 가정해보겠습니다.

이렇게 되면 각각의 커패시터는 고유의 공진 주파수를 갖습니다.

- C1의 공진 주파수: f₁ (낮음)

- C2의 공진 주파수: f₂ (높음)

그리고 중간 주파수 영역에서는 어떤 일이?

f₁과 f₂ 사이 주파수 대역에서는 두 커패시터의 ESL이 서로 영향을 주면서 병렬 공진이 발생합니다.

이 병렬 공진은 의도하지 않았던 임피던스 상승을 유발할 수도 있고, 때론 이를 이용해 특정 주파수의 억제를 설계에 반영할 수도 있습니다.

주의할 점은 병렬이 무조건 좋은 건 아닙니다?

맞습니다.

무작정 병렬로만 늘린다고 좋은 건 아닙니다.

- 패턴 길이 짧게: 커패시터는 IC 가까이에, 최대한 짧은 경로로 연결해야 ESL 효과가 극대화됩니다.

- 공진 주파수 간섭 고려: 의도치 않은 병렬 공진(anti-resonance)은 오히려 특정 주파수에서 임피던스를 급격히 올릴 수 있으므로 주의해야 합니다.

- 다양한 용량 조합 필수: 같은 용량만 병렬로 쓰는 것보다, 다양한 용량을 조합해 각 주파수 대역을 나눠 커버하는 게 더 효율적입니다.

디커플링 커패시터를 병렬로 사용하는 전략은 단순한 기술 트릭이 아니라, 고속 디지털 회로의 전원 품질을 유지하기 위한 핵심 설계 기법입니다.

- “큰 용량은 저주파용, 작은 용량은 고주파용”

- “서로 다른 커패시터는 서로 다른 역할을 가진다”

이 두 가지 문장을 기억해두시면, 향후 어떤 시스템이든 안정적인 전원 설계에 훨씬 유리해질 겁니다.

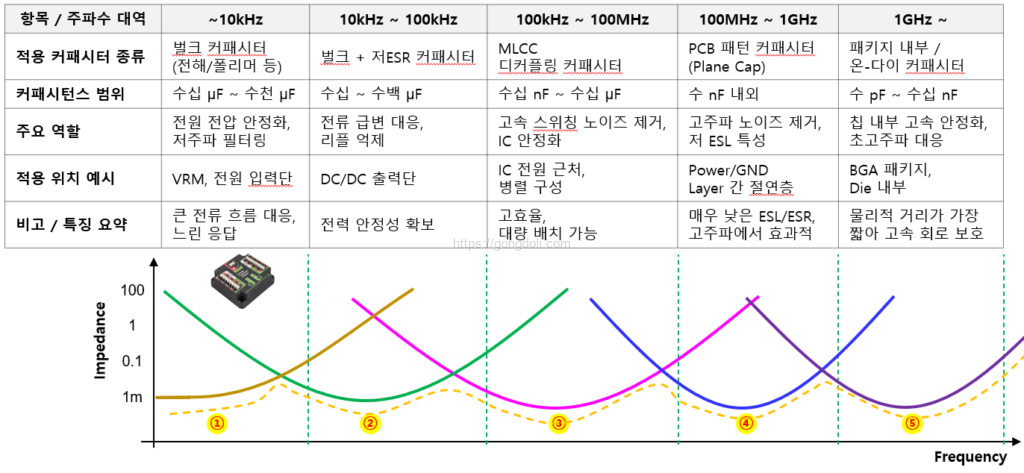

5. 주파수 대역 별 Cap 역할

회로 설계에서 전원 품질(Power Integrity, PI)은 단순한 안정성의 문제를 넘어서 고속 신호의 정확도와 시스템 전체의 신뢰성에 직접적인 영향을 줍니다.

특히 디커플링 커패시터는 이 전원 품질을 지탱하는 핵심 요소 중 하나입니다.

그런데 많은 초보 엔지니어들이 한 가지 오해하는 부분이 있습니다.

바로 “0.1μF 하나면 충분하지 않나요?” 하는 질문입니다.

실제로는 전혀 그렇지 않습니다.

왜 여러 종류의 커패시터가 필요할까?현실의 커패시터에는 ESL(등가 직렬 인덕턴스)과 ESR(등가 직렬 저항)이 존재합니다.

이로 인해 각 커패시터는 고유한 자체 공진 주파수를 가지게 되며, 그 주파수를 기준으로 커패시터는 커패시턴스 특성을 잃고 오히려 인덕턴스 성질을 띠게 됩니다.

즉, 아래와 같은 ‘V’자 형태의 임피던스 곡선을 가지게 되는 거죠.

따라서 전체 전원 선로에서 넓은 주파수 대역을 커버하려면 다양한 용량, 다양한 패키지 구조를 가진 커패시터들이 적절히 배치되어야 합니다.

우리가 흔히 말하는 디커플링 커패시터는 실제로는 더 넓은 전원 구조의 일부입니다.

디커플링 커패시터는 단일 커패시터로 모든 주파수를 커버할 수 없습니다.

그래서 위 표처럼 다양한 주파수 대역을 각각 담당하는 커패시터들을 적절히 배치해야 합니다.

- 저주파 대역 (~100kHz)는 주로 전류가 부족할 때를 대비한 “비상 전력 공급” 느낌입니다.

이때는 벌크 커패시터가 전류의 완충 작용을 하며 시스템을 안정시켜 줍니다. - 100kHz ~ 100MHz는 거의 모든 디지털 IC에서 가장 활발하게 스위칭이 일어나는 구간입니다.

이 영역은 디커플링 커패시터가 담당해야 하고, 되도록 IC 가까이에 다수 배치하는 게 핵심입니다. - 100MHz를 넘어서면, 일반 커패시터의 ESL이 문제가 되기 시작합니다.

이때는 PCB 자체의 패턴 커패시터가 활약합니다.

이건 MLCC보다도 ESL이 더 낮아서 고주파에 유리합니다. - 1GHz 이상에서는 칩 내부의 커패시터가 거의 최후의 보루처럼 작동합니다.

칩 내부에서 동작하는 회로들을 가장 가까운 위치에서 보호해 줍니다.

결국, 이 모든 조합이 잘 설계되어야 전원 선로의 임피던스를 넓은 주파수 범위에서 낮게 유지할 수 있습니다.

이렇게 전원 구조를 계층적으로 보면, 각 단계는 서로 다른 주파수 대역의 잡음을 필터링하며, 전체 전원 임피던스를 최소화하기 위해 협력합니다.