Contents

1. 디지털 비교기란?

1-1) 디지털 비교기의 정의와 기본 개념

디지털 비교기는 두 개의 디지털 입력 값을 비교하여 그 값의 크기를 판단하는 회로입니다.

주로 ‘A > B’, ‘A = B’, ‘A < B’와 같은 비교 결과를 출력합니다.

디지털 비교기 회로 설계는 전자 회로 설계에서 중요한 부분으로, 특히 디지털 시스템에서 많이 사용됩니다.

비교기는 두 개 이상의 입력 값을 받아 그 값의 관계를 결정하여 특정 조건에 따라 출력 신호를 생성합니다.

1-2) 디지털 비교기의 주요 기능과 역할

디지털 비교기의 주요 기능은 두 개의 디지털 값을 비교하여 다음과 같은 세 가지 결과를 출력하는 것입니다.

- ‘A > B’: 첫 번째 입력 값(A)이 두 번째 입력 값(B)보다 클 때 출력.

- ‘A = B’: 첫 번째 입력 값(A)과 두 번째 입력 값(B)이 같을 때 출력.

- ‘A < B’: 첫 번째 입력 값(A)이 두 번째 입력 값(B)보다 작을 때 출력.

이러한 기능은 디지털 비교기 회로 설계를 통해 구현됩니다.

비교기는 마이크로프로세서, 마이크로컨트롤러, 메모리 모듈 등 다양한 디지털 시스템에서 필수적인 요소로 사용됩니다.

예를 들어, 데이터 정렬, 주소 비교, 순위 결정 등 다양한 응용 분야에서 핵심적인 역할을 합니다.

1-3) 디지털 비교기의 응용 분야

디지털 비교기는 여러 응용 분야에서 사용됩니다.

- 데이터 정렬 : 비교기는 데이터 정렬 알고리즘에서 중요한 역할을 합니다.

비교기를 사용하여 데이터의 크기를 비교하고, 이를 바탕으로 데이터를 정렬합니다. - 주소 비교 : 마이크로프로세서나 메모리 시스템에서 주소 비교기는 특정 주소에 대한 접근을 제어하는 데 사용됩니다.

- 계수기 : 비교기는 계수기 회로에서 특정 값을 초과했는지 여부를 판단하는 데 사용됩니다.

예를 들어, 특정 값에 도달하면 알람을 울리거나 특정 동작을 수행할 수 있습니다. - 제어 시스템 : 비교기는 제어 시스템에서 특정 조건을 충족하는지 확인하고, 조건이 충족될 때 특정 동작을 트리거하는 데 사용됩니다.

이처럼 디지털 비교기는 다양한 디지털 시스템과 회로에서 중요한 역할을 합니다.

디지털 비교기 회로 설계를 통해 이와 같은 다양한 응용 분야에서 효율적이고 정확한 비교 기능을 구현할 수 있습니다.

- 연관 참조 : 이진 감산기 회로 설계, 직렬과 병렬 감산기 비교, 회로 설계 예제 3가지

- 연관 참조 : 이진 가산기 회로 설계, 회로 설계 방법, 예제 설계 2가지

- 연관 참조 : 2진 디코더 회로 설계, 회로 설계 방법, 예제,설계 문제 4가지

- 연관 참조 : Encoder 회로 설계, 회로 설계 방법, 예제, 흔한 설계 문제 4가지

- 연관 참조 : Demultiplexer 회로 설계, 회로 설계 방법, 예제, 흔한 설계 문제 5가지

- 연관 참조 : Multiplexer 회로 설계,유형과 종류,회로 설계 방법, 예제

- 연관 참조 : 조합 논리 회로, 회로 설계, 부울 대수 이용, 카르노 맵 이용,예제1

2. 디지털 비교기의 유형

3. 디지털 비교기 회로 설계 방법

3-1) 기본 설계 원리: 진리표에서 논리식으로

디지털 비교기 회로 설계는 진리표에서 논리식으로 변환하는 기본 설계 원리를 따릅니다.

진리표는 모든 가능한 입력 조합에 대한 출력을 정의한 표입니다.

이를 통해 각 입력 조합에 따른 출력을 명확히 이해할 수 있습니다.

진리표를 작성한 후, 각 출력에 대한 논리식을 도출합니다.

이러한 논리식은 AND, OR, NOT 등의 논리 게이트를 사용하여 회로로 구현할 수 있습니다.

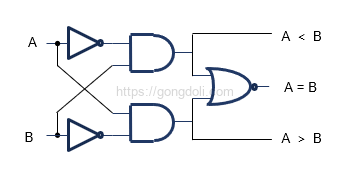

3-2) 1비트 비교기 설계

1비트 비교기는 두 개의 단일 비트를 비교하여 그 결과를 출력하는 회로입니다.

1비트 비교기에는 세 가지 결과가 있습니다

- A가 B보다 큰 경우, A와 B가 같은 경우, A가 B보다 작은 경우입니다.

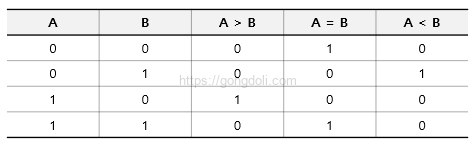

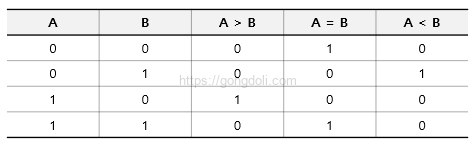

-. 진리표 작성

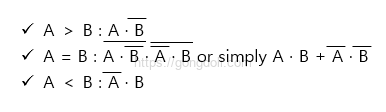

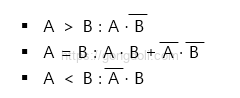

-. 논리식 도출

이 논리식을 사용하여 회로를 구성하면 됩니다.

3-3) 다중 비트 비교기 설계

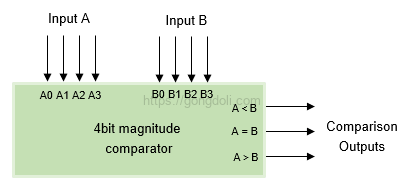

다중 비트 비교기는 여러 비트로 구성된 두 입력 값을 비교하는 회로입니다.

예를 들어, 4비트 비교기는 두 개의 4비트 입력 값을 비교하여 그 결과를 출력합니다.

각 비트의 비교 결과를 종합하여 최종 결과를 도출합니다.

다중 비트 비교기의 논리식은 매우 복잡할 수 있으며, 이를 최적화하는 방법이 필요합니다.

3-4) 디지털 비교기 회로의 최적화 기법

디지털 비교기 회로의 최적화는 다음과 같은 기법을 통해 이루어집니다.

- 카르노 맵: 진리표를 간소화하여 논리식을 최소화합니다.

- 부울 대수: 논리식을 수학적으로 간소화합니다.

- 다중 입력 논리 게이트 사용: 복잡한 논리식을 단순화하기 위해 NAND, NOR 게이트 등을 사용합니다.

- 모듈화: 큰 회로를 작은 모듈로 나누어 각 모듈을 최적화합니다.

4. 디지털 비교기 회로 설계 예제

4-1) 1비트 비교기 회로 설계 단계별 설명

1비트 비교기는 두 개의 단일 비트를 비교하여 A가 B보다 큰지, 같은지, 작은지를 출력하는 회로입니다.

1단계 : 진리표 작성

2단계 : 논리식 도출

3단계 : 회로 구성

AND 게이트와 NOT 게이트를 사용하여 도출된 논리식을 구현합니다.

A > B : A를 AND 게이트에 입력하고, B를 NOT 게이트를 거쳐 AND 게이트에 입력합니다.

A = B : 두 개의 AND 게이트를 사용하여 A와 B, A’와𝐵’를 입력하고, 그 결과를 OR 게이트로 결합합니다.

A < B : B를 AND 게이트에 입력하고, A를 NOT 게이트를 거쳐 AND 게이트에 입력합니다.

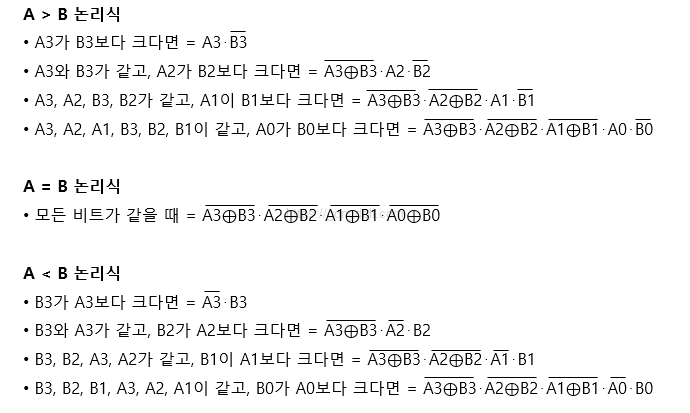

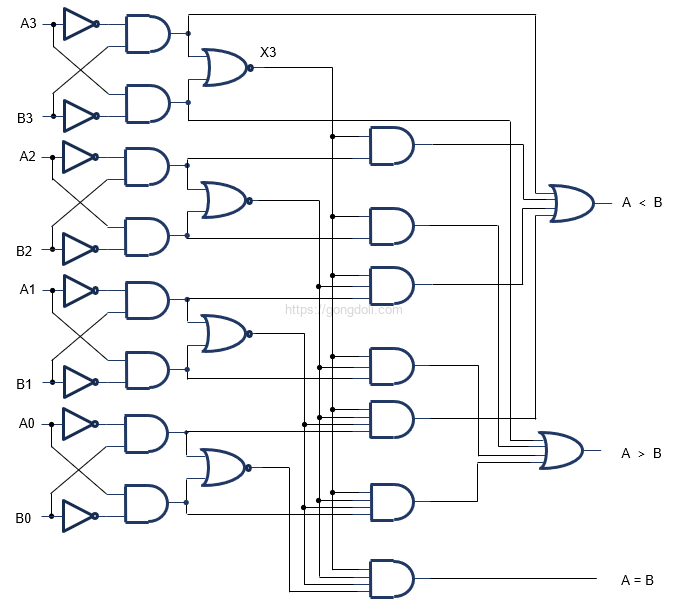

4-2) 4비트 비교기의 진리표와 회로 구현

4비트 비교기는 두 개의 4비트 값을 비교하여 A가 B보다 큰지, 같은지, 작은지를 출력하는 회로입니다.

1단계 : 진리표 작성

각각의 비트를 비교하여 결과를 도출하는 기본적인 논리를 통해 작성된 진리표는 아래와 같습니다.

2단계 : 4비트 비교기의 논리식 도출

3단계 : 4비트 비교기 회로 구성

상업적으로 사용 가능한 디지털 비교기 중에는 TTL 74LS85나 CMOS 4063과 같은 4비트 크기 비교기가 있습니다.

이러한 비교기들은 추가 입력 단자를 제공하여 여러 개의 비교기를 “연결”할 수 있게 합니다.

이를 통해 4비트보다 더 큰 단어를 비교할 수 있습니다.

예를 들어, 8비트, 16비트 또는 32비트와 같은 더 큰 단어를 비교할 때, 이러한 비교기의 연결 입력 단자는 이전 비교기의 출력 단자에 직접 연결됩니다.

이를 통해 여러 비트를 동시에 비교할 수 있는 크기 비교기가 생성됩니다.

이와 같은 기능을 통해 크기 비교기를 이용한 더 큰 데이터 단어의 비교가 가능합니다.

5. 디지털 비교기 회로 설계 주의 사항

디지털 비교기 회로 설계는 비교기의 정확성과 신뢰성을 보장하기 위해 주의가 필요합니다.

설계 과정에서 흔히 발생할 수 있는 문제와 이를 해결하기 위한 방법을 알아보겠습니다.

- 정확한 진리표 작성

디지털 비교기 회로 설계의 첫 단계는 비교기 동작을 명확히 정의하는 진리표를 작성하는 것입니다.

진리표는 입력과 출력의 모든 가능한 조합을 나열하여 각 입력 상태에 대한 출력을 명확히 합니다.

진리표 작성 시 실수를 방지하려면 모든 가능한 입력 조합을 빠짐없이 고려해야 합니다. - 전파 지연 최소화

디지털 회로에서 전파 지연은 비교 결과가 지연되어 출력에 반영되는 시간을 의미합니다.

전파 지연을 최소화하려면 논리 게이트의 수를 줄이고, 가능한 한 간단한 논리식을 사용하여 회로를 설계해야 합니다.

또한, 빠른 응답 시간을 위해 고속 논리 게이트를 사용하는 것도 좋은 방법입니다. - 입력 신호의 타이밍

입력 신호의 타이밍 문제는 디지털 비교기 회로 설계에서 중요한 요소입니다.

모든 입력 신호가 동일한 시간에 도달하지 않으면 비교 결과가 잘못될 수 있습니다.

이를 해결하기 위해 클럭 신호를 사용하여 입력 신호를 동기화하고, 플립플롭 등을 사용하여 입력을 잠금으로써 타이밍 문제를 방지할 수 있습니다. - 전력 소모 관리

디지털 비교기 회로는 여러 논리 게이트로 구성되므로 전력 소모가 클 수 있습니다.

전력 소모를 줄이기 위해서는 저전력 논리 게이트를 사용하고, 필요하지 않은 부분의 회로를 비활성화하는 등의 방법을 고려해야 합니다.

이를 통해 전력 효율성을 높일 수 있습니다. - 잡음 민감도 감소

잡음은 디지털 비교기 회로의 신뢰성에 큰 영향을 미칠 수 있습니다.

잡음에 민감한 회로를 설계하면 잘못된 비교 결과가 나올 수 있습니다.

잡음을 줄이기 위해 쉴딩, 디커플링 커패시터 사용, 신호선의 길이 최적화 등의 방법을 사용할 수 있습니다. - 레이아웃 고려

PCB 설계 시 회로의 레이아웃도 중요한 요소입니다.

전력선과 신호선을 잘 분리하고, 접지면을 넓게 사용하여 전자파 간섭을 줄이는 것이 좋습니다.

또한, 비교기 회로와 주변 회로 간의 상호 간섭을 최소화하기 위해 적절한 공간 배치와 쉴딩을 적용해야 합니다. - 테스트 및 검증

디지털 비교기 회로 설계가 완료되면 충분한 테스트와 검증이 필요합니다.

시뮬레이션을 통해 회로의 동작을 미리 검증하고, 실제 회로 제작 후에는 다양한 입력 조건에서 테스트를 수행하여 설계가 의도한 대로 동작하는지 확인해야 합니다.

위의 주의 사항을 고려하여 디지털 비교기 회로 설계를 진행하면 보다 안정적이고 신뢰성 높은 회로를 구현할 수 있습니다.

이러한 주의 사항들은 디지털 비교기 회로 설계의 핵심 요소로, 최적의 성능을 보장하기 위해 반드시 고려해야 할 사항들입니다.

Pretty! This was a really wonderful post. Thank you for your provided information.

Thank you so much for your kind words! I’m delighted you enjoyed the post and found the information valuable.

I went over this site and I conceive you have a lot of fantastic information, bookmarked (:.

Thank you so much for your kind words and for bookmarking the site!

You are my intake, I own few web logs and very sporadically run out from to post : (.

I’m honored to be a source of inspiration for you! Blogging consistently can be challenging, but I hope new ideas keep flowing your way.

Hello. impressive job. I did not anticipate this. This is a great story. Thanks!

I’m really glad you enjoyed it!

It means a lot to hear that the story surprised you in a good way.

Hi there just wanted to give you a quick heads up and let you know a few of the pictures aren’t loading correctly. I’m not sure why but I think its a linking issue. I’ve tried it in two different browsers and both show the same outcome.

Hi, thanks so much for bringing this to our attention! We’re sorry to hear that some of the images aren’t loading properly.

It does sound like it could be a linking issue, especially since you’ve tested it across multiple browsers.

We’ll look into it right away and work on resolving it.

If you happen to have any screenshots or specific image URLs that are affected, feel free to share them—it’ll help us troubleshoot faster.

Thanks again for your patience!

Howdy! I simply would like to give an enormous thumbs up for the great info you might have right here on this post. I might be coming again to your blog for extra soon.

Thank you so much for the kind words and the big thumbs up!

I’m really glad you found the post helpful.

Please let me know if you’re looking for a author for your blog. You have some really good articles and I feel I would be a good asset. If you ever want to take some of the load off, I’d love to write some material for your blog in exchange for a link back to mine. Please shoot me an email if interested. Many thanks!

Thank you for your generous offer and kind words!

I truly appreciate your interest in contributing to the blog.

At the moment, we’re not actively seeking guest authors, but I’ll definitely keep your proposal in mind for future opportunities.

Wishing you continued success with your own blog

Great paintings! That is the type of info that are meant to be shared around the net. Disgrace on the search engines for not positioning this post higher! Come on over and seek advice from my site . Thank you =)

Thank you so much!

I’m honored by your kind words and truly appreciate the support.

Only a smiling visitor here to share the love (:, btw outstanding pattern. “Everything should be made as simple as possible, but not one bit simpler.” by Albert Einstein.

Thank you!

Woh I like your posts, saved to favorites! .

Thank you so much! I’m glad you enjoyed the posts.

I went over this web site and I think you have a lot of good information, saved to bookmarks (:.

Thank you! I’m glad you found the information useful and bookmarked the site.

I’m not that much of a internet reader to be honest but your blogs really nice, keep it up! I’ll go ahead and bookmark your site to come back later on. Many thanks

Thank you! I’m glad you enjoyed the blog and plan to come back later.

Thanks a lot for sharing this with all of us you actually know what you’re talking about! Bookmarked. Kindly also visit my web site =). We could have a link exchange agreement between us!

Thank you very much for your kind words and support. I truly appreciate you bookmarking the site. I’ll be happy to check out your website as well.

F*ckin’ amazing issues here. I am very satisfied to peer your post. Thank you a lot and i’m having a look ahead to touch you. Will you please drop me a mail?

Thank you so much for your enthusiastic feedback. I truly appreciate your support. At the moment, I don’t provide direct email contact, but I’m glad you’re enjoying the posts and I’ll keep sharing more here.

I like what you guys are up also. Such smart work and reporting! Keep up the superb works guys I¦ve incorporated you guys to my blogroll. I think it’ll improve the value of my website 🙂

Thank you for adding us to your blogroll.

You are my inspiration , I own few web logs and rarely run out from to brand : (.

Thank you, I’m honored to be your inspiration.

Very interesting information!Perfect just what I was searching for! “The most wasted day of all is that on which we have not laughed.” by Sbastien-Roch Nicolas de Chamfort.

Thank you! I’m glad the information was helpful

Greetings! Very helpful advice on this article! It is the little changes that make the biggest changes. Thanks a lot for sharing!

Thank you for your thoughtful comment! I’m glad you found it helpful.

It’s a pity you don’t have a donate button! I’d definitely donate to this outstanding blog! I suppose for now i’ll settle for bookmarking and adding your RSS feed to my Google account. I look forward to new updates and will share this website with my Facebook group. Chat soon!

Thank you so much for your generous support! I truly appreciate your kind words, and sharing the site means a lot.