1. 순차 논리 회로란?

1-1) 정의 및 개요

순차 논리 회로(Sequential Logic Circuit) 는 디지털 회로의 한 종류로, 시간의 흐름과 이전 상태에 따라 출력이 결정되는 회로입니다.

이는 단순히 입력에 의해서만 출력이 결정되는 조합 논리 회로(Combinational Logic Circuit)와는 달리, 입력 외에 내부 상태를 저장하고 그에 따라 동작을 변경합니다.

순차 논리 회로 설계는 클럭 신호(Clock Signal)라는 주기적인 신호에 의해 동작합니다.

클럭 신호는 회로의 상태가 변하는 순간을 결정하며, 이 신호에 따라 회로는 새로운 상태로 전이합니다.

따라서, 순차 논리 회로 설계는 시간의 흐름에 따라 순차적으로 상태가 변한다고 해서 “순차적”이라는 이름이 붙었습니다.

쉽게 이해할 수 있는 예로 자판기를 생각해 보겠습니다.

자판기는 사용자의 입력(동전 투입 및 상품 선택)에 따라 작동합니다.

자판기가 몇 번의 동전이 투입되었는지 기억해야 하며, 이 기억된 정보를 기반으로 올바른 작동을 합니다.

이는 단순히 입력만으로 작동하지 않으며, 과거 상태(이미 투입된 동전 수)에 의존합니다.

바로 이 점이 순차 논리 회로의 핵심입니다.

순차 논리 회로 설계는 내부적으로 플립플롭(Flip-Flop) 또는 래치(Latch) 같은 저장 요소를 사용하여 상태 정보를 저장합니다.

이런 상태 저장 장치들은 현재의 회로 상태를 보존하고, 다음 클럭 신호가 올 때까지 이 상태를 유지합니다.

이렇게 저장된 정보는 다음 클럭 신호에 의해 업데이트되며, 이를 통해 회로는 시간에 따른 상태 변화를 관리합니다.

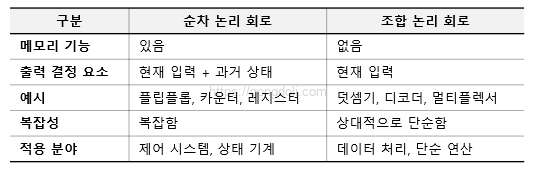

1-2) 조합 논리 회로와의 차이점

순차 논리 회로와 조합 논리 회로를 비교하면 그 차이를 명확하게 이해할 수 있습니다.

- 조합 논리 회로(Combinational Logic Circuit)는 즉시적으로 동작합니다.

즉, 입력 신호가 변하면 그에 따른 출력이 즉시 결정됩니다.

과거의 상태나 이전 입력과는 무관하게 현재 입력에만 의존하여 출력이 결정됩니다.

예를 들어, 디지털 논리 게이트(AND, OR, NOT 등)는 조합 논리 회로의 일종입니다.

AND 게이트는 두 입력이 모두 ‘1’일 때만 출력이 ‘1’이 되며, 이 상태는 과거의 입력과는 무관하게 현재 입력에 의해 즉시 결정됩니다. - 순차 논리 회로(Sequential Logic Circuit)는 상태 정보와 시간적 요소를 고려합니다.

즉, 현재 입력뿐만 아니라 과거의 상태(내부 상태 저장 장치에 저장된 정보)도 출력 결정에 영향을 미칩니다.

이는 회로가 시간에 따라 동작을 기억하고, 변화할 수 있다는 것을 의미합니다.

시계를 예로 들어보겠습니다.

시계는 단순히 현재 시간(입력)을 표시하는 것만으로는 충분하지 않습니다.

이전 시간(과거 상태)을 기반으로 현재 시간을 계산하고, 다음 시간을 예측합니다.

시계는 현재 시간이 몇 시인지에 따라 분침과 시침의 위치를 조정합니다.

이처럼, 시간의 흐름과 상태를 기억하는 능력이 순차 논리 회로 설계의 본질입니다.

다시 정리하자면, 순차 논리 회로는 시간의 흐름과 이전 상태에 의존하여 동작하는 디지털 회로입니다.

이를 통해 복잡한 동작을 수행하고, 상태를 관리할 수 있습니다.

반면, 조합 논리 회로는 현재 입력만을 고려하여 즉시 출력을 결정하는 회로입니다.

이러한 차이는 순차 논리 회로가 보다 복잡하고 유연한 동작을 가능하게 합니다.

순차 논리 회로는 컴퓨터, 프로세서, 메모리 시스템 등 다양한 분야에서 중요한 역할을 합니다.

이는 시간이 지남에 따라 상태를 추적하고 제어할 수 있어야 하기 때문입니다.

- 연관 참조 :시프트 레지스터 동작 원리, 정의, 종류 4가지, SISO, SIPO, PISO, PIPO

- 연관 참조 : D 플립플롭 동작 원리,정의, 구조, 동작 원리

- 연관 참조 : JK 플립플롭 동작 원리, 구조, 동작 원리, 장.단점, 설계 예시

2. 순차 논리 회로의 구성 요소

순차 논리 회로 설계는 현재 상태와 입력 신호에 따라 출력을 생성하며, 상태를 저장하는 능력을 가진 디지털 회로입니다.

이 회로의 기본 구성 요소는 래치(Latch), 플립플롭(Flip-Flop), 클럭 신호(Clock Signal), 그리고 상태 저장(State Storage) 및 상태 전이(State Transition)입니다.

2-1) 래치(Latch)와 플립플롭(Flip-Flop)의 기초

래치(Latch)와 플립플롭(Flip-Flop)은 순차 논리 회로 설계의 핵심 메모리 요소로, 회로의 상태를 저장하는 역할을 합니다.

이들은 회로의 과거 정보를 유지하여 시간에 따라 변화하는 입력과 상태를 관리합니다.

2-1-1) 래치(Latch)

래치는 입력 신호의 변화에 따라 즉시 상태를 변경하는 메모리 소자입니다.

래치는 클럭 신호 없이도 작동할 수 있으며, 입력 신호가 바뀌면 즉시 상태를 업데이트합니다.

가장 기본적인 형태의 래치는 SR 래치(SR Latch)로, Set과 Reset 입력을 통해 저장 상태를 제어합니다.

- SR 래치의 동작 원리

Set(S) 입력이 활성화되면, 래치는 출력이 1로 설정됩니다.

Reset(R) 입력이 활성화되면, 래치는 출력이 0으로 설정됩니다.

둘 다 비활성화된 상태에서는, 래치는 이전 상태를 유지합니다.

동시에 활성화(S=R=1)되는 경우는 금지 상태로, 예기치 않은 동작이 발생할 수 있습니다.

SR 래치는 작은 메모리 소자로 사용되며, 여러 종류의 래치를 구성하는 기본 블록으로 사용됩니다.

2-1-2) 플립플롭(Flip-Flop)

플립플롭은 클럭 신호에 동기화되어 작동하는 메모리 소자입니다.

래치와 달리, 플립플롭은 클럭 신호의 상승 또는 하강 에지(edge)에서만 상태를 변경합니다.

이 특성 때문에 플립플롭은 안정적인 상태 전이와 동기화가 필요한 순차 논리 회로 설계에 주로 사용됩니다.

가장 일반적인 형태의 플립플롭은 D 플립플롭(D Flip-Flop)입니다.

- D 플립플롭의 동작 원리

D 입력은 다음 상태에 저장될 값을 제공합니다.

클럭 신호가 상승 에지를 가질 때, D 입력의 값이 출력 Q로 전송되어 저장됩니다.

다른 순간에는 D 입력의 변화가 출력에 영향을 미치지 않습니다.

D 플립플롭은 입력 데이터를 저장하고, 클럭 신호에 동기화하여 동작하는 데 적합합니다.

이 때문에 레지스터, 카운터, 시프트 레지스터 등의 설계에 많이 사용됩니다.

2-1-3) 래치와 플립플롭의 비교

순차 논리 회로 설계에서는 플립플롭을 주로 사용하여 안정적인 동작을 구현합니다.

플립플롭의 동기화된 특성 덕분에 복잡한 회로 설계에서 타이밍 문제를 해결할 수 있습니다.

2-2) 클럭 신호(Clock Signal)와 동기화

순차 논리 회로 설계의 또 다른 중요한 요소는 클럭 신호(Clock Signal)입니다.

클럭 신호는 회로의 모든 동작을 동기화하는 역할을 하며, 회로가 일정한 주기로 동작하도록 만듭니다.

- 클럭 신호의 역할

동기화(Synchronization) : 클럭 신호는 회로 내 모든 플립플롭의 상태 전이를 동기화하여 일관성 있는 동작을 보장합니다.

상태 전이 제어 : 클럭 신호의 에지에서만 상태가 변경되도록 하여, 비정상적인 상태 변화와 레이스 컨디션(Race Condition)을 방지합니다.

클럭 신호는 주로 정사각형 파형(square wave)으로 생성되며, 일정한 주기와 주파수를 가집니다.

클럭 주파수는 회로의 동작 속도를 결정하며, 설계자는 주어진 응용 분야에 맞는 적절한 클럭 주파수를 선택해야 합니다.

동기화된 회로 설계는 신뢰성과 안정성을 높이는 데 필수적입니다.

예를 들어, 컴퓨터의 중앙 처리 장치(CPU)에서는 클럭 신호를 이용하여 모든 연산과 데이터 전송을 동기화합니다.

이로 인해 데이터의 정확한 처리와 동작이 가능해집니다.

2-3) 상태 저장(State Storage)과 상태 전이(State Transition)

순차 논리 회로 설계에서 상태 저장과 상태 전이는 핵심적인 개념입니다.

상태 저장은 회로가 이전에 어떤 상태였는지를 기억하는 것이고, 상태 전이는 현재 상태와 입력에 따라 다음 상태로 변화하는 것입니다.

- 상태 저장(State Storage)

상태 저장은 플립플롭이나 래치와 같은 메모리 요소를 통해 이루어집니다.

이들은 회로의 현재 상태를 유지하며, 이후 상태 전이와 출력 결정에 사용됩니다. - 상태 전이(State Transition)

상태 전이는 입력과 현재 상태를 기반으로 다음 상태가 결정되는 과정입니다.

이 과정은 상태 다이어그램(State Diagram)이나 상태 전이 표(State Transition Table)를 통해 설계됩니다.

상태 저장과 상태 전이는 다양한 응용 분야에서 중요한 역할을 합니다.

예를 들어, 교통 신호등 제어 시스템에서는 각 신호등의 상태를 저장하고, 차량 감지 센서 입력에 따라 신호등이 적절히 변화하도록 상태 전이를 설계합니다.

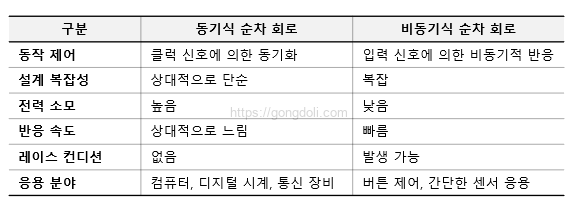

3. 순차 논리 회로의 종류

순차 논리 회로는 입력과 저장된 상태에 따라 출력을 결정하는 디지털 회로로, 주로 두 가지 유형으로 구분됩니다.

동기식 순차 회로(Synchronous Sequential Circuit)와 비동기식 순차 회로(Asynchronous Sequential Circuit)입니다.

각 유형은 동작 방식과 응용 분야에서 차이가 있으며, 순차 논리 회로 설계 시 고려해야 할 중요한 요소들입니다.

3-1) 동기식 순차 회로(Synchronous Sequential Circuit)

동기식 순차 회로는 클럭 신호(Clock Signal)를 사용하여 회로 내 모든 메모리 요소의 상태 전이를 동기화하는 방식으로 동작합니다.

이 회로는 클럭 신호의 에지(상승 에지 또는 하강 에지)에서만 상태 전이가 발생하므로, 일관성 있는 동작과 안정성을 보장할 수 있습니다.

-. 동기식 순차 회로의 동작 원리

- 클럭 신호에 의한 제어 : 동기식 순차 회로는 일정한 주기의 클럭 신호에 의해 모든 플립플롭이 동시에 상태를 갱신합니다.

이로 인해 회로 내의 모든 상태 전이가 동시에 발생하며, 이는 예측 가능하고 제어 가능한 시스템을 구축하는 데 유리합니다. - 상태 저장 : 플립플롭이 사용되며, 클럭 신호의 에지에서만 입력이 저장되기 때문에 입력의 불규칙한 변화에 의해 발생할 수 있는 불안정한 상태 변화를 방지할 수 있습니다.

예를 들어, 디지털 시계는 동기식 순차 회로의 한 예입니다.

시계는 일정한 주기의 클럭 신호를 받아 초, 분, 시간 등을 카운트합니다.

이 과정은 클럭 신호에 의해 정확하게 동기화되어 있어 시간의 경과에 따른 정확한 상태 전이가 보장됩니다.

-. 동기식 순차 회로의 장단점

- 장점

예측 가능한 동작: 클럭 신호에 의해 동작이 동기화되므로 시스템의 상태 전이가 예측 가능하고 일관성 있습니다.

설계의 용이성: 상태 전이 시점을 명확히 알 수 있어 회로 설계 및 디버깅이 용이합니다.

잡음에 대한 내성: 클럭 신호에 의한 동기화는 입력의 불규칙한 변화에 대한 내성을 증가시킵니다. - 단점

클럭 신호 필요: 클럭 신호 생성과 배분이 필요하며, 이는 설계의 복잡성을 증가시킬 수 있습니다.

전력 소모: 모든 플립플롭이 클럭 신호를 필요로 하므로 전력 소모가 상대적으로 높습니다.

동기식 순차 회로 설계는 주로 클럭 신호가 존재하는 시스템에서 안정적이고 일관된 동작이 필요할 때 선택됩니다.

3-2) 비동기식 순차 회로(Asynchronous Sequential Circuit)

비동기식 순차 회로는 클럭 신호 없이 입력의 변화에 따라 즉시 상태 전이가 발생하는 방식으로 동작합니다.

이는 상태 전이가 클럭 신호에 의해 제어되지 않고 입력 신호에 직접적으로 반응하기 때문에, 비동기식 회로는 더 빠르게 반응할 수 있는 장점이 있습니다.

-. 비동기식 순차 회로의 동작 원리

- 입력 신호에 의한 제어 : 비동기식 회로는 입력의 변화에 즉시 반응하여 상태가 변합니다.

이로 인해 클럭 신호에 의해 제약받지 않으며, 반응 속도가 매우 빠릅니다. - 레이스 컨디션 : 입력의 변화가 불규칙하고 연속적으로 발생할 경우, 상태 전이가 예상치 못한 방식으로 이루어질 수 있습니다.

이를 레이스 컨디션(Race Condition)이라고 하며, 이는 회로의 안정성을 해칠 수 있는 문제로 작용할 수 있습니다.

간단한 버튼 제어 회로를 예로 들 수 있습니다.

버튼을 누르면 즉시 상태가 변하여 LED가 켜지거나 꺼지는 방식입니다.

이처럼 입력의 즉시적인 변화에 따라 빠르게 반응하는 것이 비동기식 순차 회로의 특징입니다.

-. 비동기식 순차 회로의 장단점

- 장점

빠른 반응 속도: 입력 신호에 즉시 반응할 수 있어, 빠른 응답이 필요한 시스템에 적합합니다.

클럭 신호 불필요: 클럭 신호가 필요하지 않아 전력 소모가 적고, 회로 설계가 간단해질 수 있습니다. - 단점

레이스 컨디션: 입력의 비동기적 변화로 인해 레이스 컨디션이 발생할 수 있으며, 이는 회로의 안정성을 저하시킬 수 있습니다.

복잡한 설계: 상태 전이를 예측하기 어려워 설계 및 디버깅이 복잡할 수 있습니다.

비동기식 순차 회로 설계는 클럭 신호가 없거나 빠른 반응이 요구되는 시스템에서 사용됩니다.

3-3) 차이점과 각각의 장단점

동기식 순차 회로와 비동기식 순차 회로는 각각의 특징과 장단점이 있으며, 설계 목적에 따라 선택이 달라집니다.

동기식 순차 논리 회로 설계는 시스템의 안정성 및 일관성을 보장하며, 전력 소모를 감수하고라도 예측 가능한 동작을 원하는 경우에 적합합니다.

반면에 비동기식 순차 회로 설계는 빠른 응답이 필요하거나 전력 소모를 최소화해야 할 때 유리합니다.

각각의 회로는 상황에 맞는 적절한 설계를 통해 최적의 성능을 발휘할 수 있습니다.

4. 순차 논리 회로 설계 방법

순차 논리 회로 설계의 일반적인 설계 방법은 상태 표를 이용한 설계, 플립플롭의 선택과 상태 인코딩, 그리고 하드웨어 기술 언어(HDL)를 통한 설계를 포함합니다.

4-1) 상태 표를 이용한 설계

상태 표(State Table)는 순차 논리 회로 설계에서 가장 기본적이고 중요한 도구 중 하나입니다.

상태 표는 시스템의 모든 가능한 상태와 각 상태에서의 입력, 출력, 다음 상태를 명확히 정의하는 표입니다.

- 상태 표의 구성 요소

현재 상태(Current State): 회로의 현재 상태를 나타내는 부분입니다.

보통 이진수로 표현됩니다.

입력(Input): 현재 상태에서의 입력 조건을 나타냅니다.

다음 상태(Next State): 현재 상태와 입력 조건에 따라 전이될 다음 상태를 정의합니다.

출력(Output): 각 상태 및 입력 조건에 따른 회로의 출력을 나타냅니다.

예를 들어, 간단한 2비트 업 카운터의 상태 표를 작성해 보겠습니다.

2비트 업 카운터는 입력 클럭 펄스에 따라 상태가 순차적으로 증가하는 카운터입니다.

상태 표를 작성하면 다음과 같습니다.

- 현재 상태 (Q1Q0): 현재 카운터의 상태입니다.

- 입력 (Clk) : 클럭 신호 입력입니다. 카운터는 클럭 신호의 상승 에지에서만 상태가 전이됩니다.

- 다음 상태: 현재 상태에서 클럭 펄스가 입력되었을 때의 다음 상태입니다.

- 출력: 이 예제에서는 단순히 상태 변화만을 다루기 때문에 출력은 상태에 관계없이 0으로 설정되어 있습니다.

-. 상태 표를 이용한 설계 과정

- 문제 정의: 시스템의 요구사항을 명확히 이해하고 분석합니다.

- 상태 정의: 시스템의 가능한 모든 상태를 정의합니다.

- 상태 전이 설계: 각 상태에서의 입력에 따른 상태 전이를 정의하여 상태 표를 작성합니다.

- 출력 설계: 각 상태에서의 출력 동작을 정의합니다.

- 회로 구현: 상태 표에 따라 플립플롭 및 조합 논리 회로를 설계하여 구현합니다.

상태 표를 통한 순차 논리 회로 설계는 시스템의 동작을 명확히 정의할 수 있어, 회로의 동작을 쉽게 예측하고 검증할 수 있습니다.

4-2) 플립플롭의 선택과 상태 인코딩

플립플롭(Flip-Flop)은 순차 논리 회로 설계의 상태를 저장하는 기본 요소로, 회로 설계 시 플립플롭의 선택과 상태 인코딩은 매우 중요합니다.

적절한 플립플롭의 선택과 상태 인코딩은 회로의 효율성을 높이고, 설계의 복잡성을 줄이는 데 기여합니다.

4-2-1) 플립플롭의 선택

플립플롭의 종류는 여러 가지가 있으며, 설계 요구사항에 따라 적절한 플립플롭을 선택해야 합니다.

주로 사용되는 플립플롭은 다음과 같습니다.

- D 플립플롭: 단순한 데이터 저장에 적합하며, 대부분의 순차 논리 회로 설계에서 많이 사용됩니다.

- JK 플립플롭: T 플립플롭처럼 토글 동작을 지원하며, 상태 전이가 복잡한 회로에 적합합니다.

- T 플립플롭: 카운터 설계 등에 사용되며, 입력이 토글 신호로 작동합니다.

플립플롭을 선택할 때는 회로의 특성과 요구사항을 고려하여, 가장 적합한 플립플롭을 선택해야 합니다.

4-2-2) 상태 인코딩(State Encoding)

순차 논리 회로 설계에서 상태 인코딩은 각 상태를 이진수로 표현하는 과정입니다.

상태 인코딩 방식은 회로의 복잡성, 메모리 사용량 등에 영향을 미치며, 효율적인 설계를 위해 적절한 인코딩 방식을 선택해야 합니다.

-. 일반적인 상태 인코딩 방법

- 직접 인코딩(Direct Encoding): 각 상태를 고유한 이진수로 인코딩합니다.

상태의 수가 적을 때 유리합니다. - 이진 인코딩(Binary Encoding): 상태를 최소 비트 수의 이진수로 인코딩합니다.

비트 수가 적어 회로의 복잡성을 줄일 수 있습니다. - 그레이 코드 인코딩(Gray Code Encoding): 인접한 상태 간의 비트 전이가 최소화되도록 인코딩합니다.

전이 과정에서 오류를 줄일 수 있습니다. - 하나의 핫 인코딩(One-Hot Encoding): 각 상태를 하나의 플립플롭으로 인코딩하여, 하나의 상태에서만 1이 되도록 합니다.

상태 전이가 명확하고 디버깅이 쉬운 장점이 있지만, 플립플롭의 수가 많아질 수 있습니다.

상태 인코딩은 회로의 효율성을 높이고, 상태 전이를 명확하게 정의할 수 있도록 도와줍니다.

4-3) 하드웨어 기술 언어(HDL)를 통한 설계

하드웨어 기술 언어(HDL, Hardware Description Language)는 디지털 회로를 설계하고 구현하는 데 사용되는 프로그래밍 언어입니다.

주요 HDL로는 VHDL과 Verilog가 있으며, 복잡한 회로 설계를 자동화하고 검증하는 데 효과적으로 사용됩니다.

- HDL을 통한 설계의 장점

설계 자동화: HDL은 디지털 회로를 코드로 작성함으로써 설계를 자동화하고, 복잡한 시스템을 효율적으로 구현할 수 있습니다.

재사용 가능성: 모듈화된 설계로 코드의 재사용이 용이하며, 유지보수가 쉽습니다.

시뮬레이션 및 검증: HDL로 작성된 설계는 시뮬레이션 도구를 통해 쉽게 검증할 수 있어, 설계 오류를 사전에 발견하고 수정할 수 있습니다.

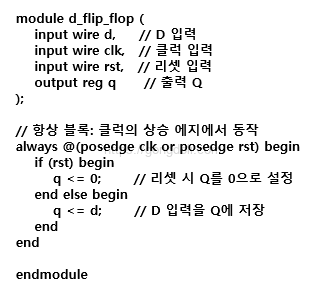

Verilog를 이용한 간단한 순차 논리 회로 설계를 예를 들어 보겠습니다.

다음은 Verilog를 사용하여 간단한 D 플립플롭을 설계한 예시입니다.

위의 코드는 D 플립플롭의 동작을 Verilog로 표현한 것입니다.

클럭의 상승 에지에서 D 입력의 값을 Q에 저장하며, 리셋 신호가 활성화되면 Q는 0으로 초기화됩니다.

이처럼 HDL을 사용하면 복잡한 순차 논리 회로 설계를 효율적으로 구현할 수 있습니다.

- HDL 설계의 과정

요구사항 분석: 설계할 회로의 요구사항을 명확히 이해합니다.

모듈 정의: 설계할 회로를 모듈 단위로 정의합니다.

HDL 코딩: 각 모듈의 동작을 HDL로 작성합니다.

시뮬레이션 및 검증: 작성된 HDL 코드를 시뮬레이션하여 동작을 검증합니다.

합성 및 구현: 설계된 회로를 실제 하드웨어에 구현합니다.

HDL을 이용한 순차 논리 회로 설계는 복잡한 시스템을 효과적으로 구현하고, 다양한 응용 분야에 맞춰 최적의 성능을 발휘할 수 있습니다,

Outstanding post, you have pointed out some great points, I besides conceive this s a very great website.

Thank you for your kind feedback! I’m so glad you find the post and website valuable

I’ve been surfing online greater than three hours as of late, yet I never discovered any attention-grabbing article like yours. It?¦s beautiful worth enough for me. In my opinion, if all webmasters and bloggers made good content material as you did, the internet will likely be a lot more helpful than ever before.

Thank you so much for your thoughtful and encouraging words! It’s incredibly rewarding to know that you find the content engaging and valuable.

We are a group of volunteers and starting a new scheme in our community. Your web site offered us with valuable info to work on. You have done a formidable job and our entire community will be thankful to you.

thank you! I’m honored that the information on the site was helpful for your initiative.

You got a very fantastic website, Sword lily I observed it through yahoo.

Thank you so much for the kind words!

I like what you guys are up also. Such smart work and reporting! Keep up the superb works guys I have incorporated you guys to my blogroll. I think it’ll improve the value of my website 🙂

Thank you so much for your kind support!

It’s an honor to be added to your blogroll, and we’re thrilled that you find value in our work.

Good website! I truly love how it is easy on my eyes and the data are well written. I’m wondering how I could be notified when a new post has been made. I have subscribed to your feed which must do the trick! Have a great day!

Thank you so much for the kind words!

I’m really glad the site feels easy to read and the content is helpful.

That is the right weblog for anyone who wants to seek out out about this topic. You notice so much its virtually arduous to argue with you (not that I actually would want…HaHa). You definitely put a brand new spin on a subject thats been written about for years. Nice stuff, just nice!

Really appreciate that—thanks for noticing the fresh perspective!

I must convey my respect for your kindness supporting people who really want assistance with your field. Your personal commitment to passing the message all-around had become extremely good and has in most cases enabled somebody just like me to arrive at their ambitions. Your entire invaluable publication entails a great deal a person like me and even more to my mates. Regards; from all of us.

Truly grateful—your words mean a lot!

Thanks for sharing excellent informations. Your website is very cool. I’m impressed by the details that you?¦ve on this blog. It reveals how nicely you perceive this subject. Bookmarked this web page, will come back for more articles. You, my pal, ROCK! I found just the info I already searched all over the place and just could not come across. What a great web-site.

Thank you so much!

I truly appreciate your kind words and support.

You made some good points there. I did a search on the topic and found most people will go along with with your website.

Thank you! I’m glad the points resonated

I also conceive thence, perfectly written post! .

Thank you! I’m glad you think the post was well written.

I think this website has some rattling fantastic information for everyone : D.

Thank you for your kind words. I’m glad you find the information helpful