Contents

1. 시프트 레지스터란?

1-1) 시프트 레지스터의 정의

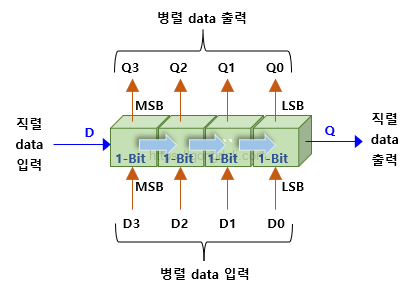

시프트 레지스터(Shift Register)는 디지털 회로에서 데이터를 순차적으로 이동하거나 저장하는 데 사용되는 기본적인 구성 요소입니다.

시프트 레지스터는 여러 개의 플립플롭(Flip-Flop)이 직렬로 연결된 형태로, 입력된 데이터를 한 비트씩 오른쪽 또는 왼쪽으로 이동시키는 기능을 수행합니다.

이 과정에서 각 플립플롭은 자신의 상태를 다음 플립플롭으로 전달하게 되며, 이를 통해 데이터가 시프트(Shift)되게 됩니다.

시프트 레지스터 동작 원리는 매우 간단합니다.

입력된 데이터가 클럭 신호에 따라 순차적으로 이동하면서, 각 단계에서 데이터를 저장하거나 출력할 수 있습니다.

이러한 동작 원리는 시프트 레지스터가 데이터 전송, 저장, 변환 등 다양한 디지털 회로에서 널리 사용되는 이유입니다.

1-2) 시프트 레지스터의 필요성

디지털 시스템에서 데이터의 이동과 저장은 매우 중요한 역할을 합니다.

시프트 레지스터는 이러한 데이터 처리 과정을 효율적으로 수행하기 위해 설계된 장치입니다.

시프트 레지스터 동작 원리에 따르면, 데이터를 직렬에서 병렬로 또는 병렬에서 직렬로 변환할 수 있어, 데이터 전송과 처리의 유연성을 제공합니다.

시프트 레지스터가 필요한 이유는 다음과 같습니다.

- 데이터 전송

시프트 레지스터는 직렬 데이터를 병렬 데이터로 변환하거나, 그 반대의 과정을 수행할 수 있습니다.

예를 들어, 시리얼 통신에서는 데이터가 한 번에 한 비트씩 전송되지만, 수신 측에서는 이 데이터를 병렬로 처리해야 할 때가 있습니다.

이때 시프트 레지스터가 데이터를 병렬로 변환하여 처리할 수 있게 해줍니다. - 데이터 저장

시프트 레지스터는 클럭 신호에 따라 데이터를 이동하면서 저장할 수 있습니다.

이를 통해 여러 비트의 데이터를 동시에 저장하고 필요한 시점에 읽어낼 수 있습니다.

예를 들어, 디지털 시스템에서 일시적인 데이터 저장이 필요한 경우, 시프트 레지스터 동작 원리를 사용하여 데이터를 안정적으로 유지할 수 있습니다. - 데이터 변환 및 제어

시프트 레지스터는 데이터를 이동시키면서 원하는 위치에 맞게 정렬하거나, 특정한 비트 패턴을 만들어낼 수 있습니다.

이는 디지털 신호 처리, 제어 회로 설계 등 다양한 분야에서 시프트 레지스터 동작 원리를 응용할 수 있게 해줍니다.

즉, 시프트 레지스터는 디지털 회로 설계에서 필수적인 구성 요소로, 데이터를 효율적으로 전송, 저장, 변환할 수 있게 해주는 중요한 장치입니다. 시프트 레지스터 동작 원리를 이해하면, 다양한 디지털 시스템에서 데이터를 보다 효율적으로 관리하고 제어할 수 있습니다.

- 연관 참조 : D 플립플롭 동작 원리,정의, 구조, 동작 원리

- 연관 참조 : JK 플립플롭 동작 원리, 구조, 동작 원리, 장.단점, 설계 예시

- 연관 참조 : 순차 논리 회로 설계, 구성, 회로의 종류, 장.단점, 설계 방법,예시

2. 시프트 레지스터 동작 원리

2-1) 데이터 이동과 저장

시프트 레지스터 동작 원리의 핵심은 데이터가 일정한 방향으로 순차적으로 이동하면서 저장되는 과정입니다.

시프트 레지스터는 여러 개의 플립플롭(Flip-Flop)을 직렬로 연결한 구조로, 입력 데이터가 클럭 신호에 따라 한 비트씩 이동하게 됩니다.

예를 들어, 4비트 시프트 레지스터가 있다고 가정해보겠습니다.

이 레지스터에 ‘1011’이라는 데이터를 입력하려면, 이 데이터는 첫 번째 클럭 신호에 의해 가장 왼쪽의 플립플롭에 저장됩니다.

다음 클럭 신호가 들어오면 첫 번째 플립플롭의 데이터는 두 번째 플립플롭으로 이동하고, 새롭게 입력된 데이터는 첫 번째 플립플롭에 저장됩니다. 이러한 과정이 계속 반복되며, 데이터는 시프트 레지스터 내에서 오른쪽으로 한 비트씩 이동하게 됩니다.

마지막으로, 데이터는 시프트 레지스터의 출력단에 도달하며, 이때 데이터를 읽어낼 수 있게 됩니다.

이러한 시프트 레지스터 동작 원리는 데이터를 저장하면서 동시에 이동할 수 있게 해줍니다.

또한, 시프트 레지스터는 데이터가 필요한 순간까지 저장되므로, 일시적인 데이터 보관이나 동기화가 필요한 상황에서도 유용하게 사용될 수 있습니다.

2-2) 동기식과 비동기식 동작 방식

시프트 레지스터는 동기식(Synchronous)과 비동기식(Asynchronous) 두 가지 방식으로 동작할 수 있습니다.

두 방식의 차이점은 데이터 이동과 저장이 클럭 신호에 어떻게 동기화되느냐에 따라 달라집니다.

동기식 시프트 레지스터에서는 모든 플립플롭이 동일한 클럭 신호에 의해 동기화됩니다.

즉, 모든 비트의 데이터 이동이 동일한 클럭 펄스에 의해 제어됩니다.

이러한 동기식 시프트 레지스터 동작 원리는 데이터가 일관되게, 그리고 예측 가능한 방식으로 이동하게 해줍니다.

이 방식은 데이터 처리 속도가 일정하고 안정적이기 때문에, 대부분의 디지털 회로 설계에서 선호됩니다.

예를 들어, 4비트 동기식 시프트 레지스터가 있다고 할 때, 클럭 신호가 한 번 발생하면 네 개의 플립플롭에 저장된 모든 비트가 동시에 오른쪽으로 이동하게 됩니다.

이로 인해 데이터 전송이 동기화되어 데이터 간의 혼란이 발생하지 않습니다.

비동기식 시프트 레지스터에서는 플립플롭 간의 동작이 클럭 신호에 의해 동기화되지 않습니다.

즉, 각 플립플롭이 독립적으로 동작하며, 데이터가 순차적으로 이동하지만 그 이동 속도는 일정하지 않을 수 있습니다.

비동기식 시프트 레지스터 동작 원리는 설계가 간단하고 하드웨어 비용이 낮은 경우에 사용되지만, 데이터 이동이 예측 불가능할 수 있어 동기식 방식에 비해 안정성이 떨어질 수 있습니다.

비동기식 시프트 레지스터 동작 원리의 예로, 첫 번째 플립플롭이 클럭 신호에 따라 데이터를 이동시키지만, 나머지 플립플롭들은 각각 자신만의 신호에 따라 동작하기 때문에 데이터가 일정하지 않은 타이밍으로 이동할 수 있습니다.

이런 방식은 간단한 제어 시스템에서 사용되지만, 정확한 타이밍이 요구되는 경우에는 적합하지 않습니다.

2. 시프트 레지스터 동작 원리 및 종류

시프트 레지스터는 데이터의 이동 방향과 출력 방식에 따라 여러 가지 형태로 구분됩니다.

각 종류의 시프트 레지스터는 특정한 데이터 처리 목적에 맞게 설계되어 있으며, 이를 통해 다양한 디지털 회로에서 효율적인 데이터 전송과 저장이 가능합니다.

아래에서 시프트 레지스터 동작 원리에 따라 구분되는 주요 네 가지 유형을 살펴보겠습니다.

3-1) 직렬 입력 직렬 출력(SISO) 시프트 레지스터

직렬 입력 직렬 출력(SISO, Serial In Serial Out) 시프트 레지스터는 가장 기본적인 형태의 시프트 레지스터로, 시프트 레지스터 동작 원리는 데이터를 하나씩 순서대로 입력받아 클럭 신호에 따라 한 비트씩 이동시키며, 최종적으로 데이터를 직렬로 출력하는 방식입니다.

이 구조는 데이터의 이동 및 처리 과정이 직관적이며, 간단한 데이터 전송이나 변환 작업에서 주로 사용됩니다.

3-1-1) 기본 원리

SISO 시프트 레지스터 동작 원리는 다음과 같습니다.

- 데이터 입력

입력 데이터는 직렬로 하나씩 시프트 레지스터의 입력 단자에 들어옵니다.

예를 들어, ‘1011’이라는 4비트 데이터를 입력하려고 할 때, 첫 번째 클럭 사이클 동안 ‘1’, 다음 클럭 사이클 동안 ‘0’, 그다음 ‘1’, 마지막으로 ‘1’이 입력됩니다. - 클럭 신호에 따른 데이터 이동

시프트 레지스터는 클럭 신호에 동기화되어 동작합니다.

각 클럭 신호가 입력될 때마다, 레지스터 내의 모든 데이터가 오른쪽으로 한 비트씩 이동합니다.

예를 들어, 4비트 SISO 시프트 레지스터의 경우, 첫 번째 클럭 신호가 입력되면 입력된 첫 번째 비트(‘1’)가 첫 번째 플립플롭에 저장됩니다.

두 번째 클럭 신호가 발생하면 첫 번째 비트는 오른쪽으로 한 칸 이동하고, 두 번째 비트(‘0’)가 첫 번째 플립플롭에 저장됩니다.

이 과정이 반복되면서, 입력된 모든 비트가 레지스터를 통해 이동하게 됩니다. - 데이터 출력

마지막 클럭 신호 이후, 시프트 레지스터에 저장된 데이터가 순차적으로 직렬 출력됩니다.

예를 들어, 네 번째 클럭 신호 이후에는 마지막 비트가 출력되고, 모든 데이터가 직렬로 출력됩니다.

3-1-2) 동작 원리 설명(예시)

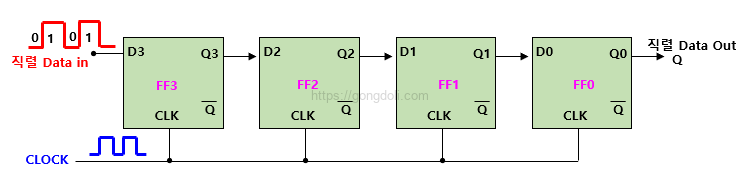

SISO 시프트 레지스터 동작 원리을 설명하기 위해 아래 그림과 같이 4개의 D 플립플롭(D0부터 D3까지)으로 구성된 회로를 생각해보겠습니다.

초기 상태에서는 모든 플립플롭이 리셋 모드에 있다고 가정합니다.

따라서 회로의 각 플립플롭의 출력은 논리 저(低) 상태, 즉 0이 됩니다.

이 회로는 우로 이동 모드(shift-right mode)로 구성되어 있다고 가정합니다.

이는 데이터 입력이 왼쪽 끝에 제공되고, 저장된 비트가 오른쪽으로 이동하여 직렬 출력으로 제공되는 것을 의미합니다.

이제 데이터가 시프트 레지스터에 어떻게 저장되는지 이해해보겠습니다.

예를 들어, ‘1111’을 시프트 레지스터에 삽입해야 한다고 가정해보겠습니다.

처음에 디바이스가 리셋 모드에 있으므로 모든 레지스터의 출력은 0입니다.

즉, 4개의 레지스터의 출력은 0000입니다.

이제 삽입할 데이터의 최하위 비트(LSB)부터 시작해봅시다.

첫 번째로 ‘1’을 회로의 입력(D3)에 제공합니다.

그러나 초기 상태에서 모든 플립플롭의 출력이 0이었기 때문에, D2, D1, D0는 여전히 0이 됩니다.

입력 D3 = 1은 Q3을 1로 설정하게 됩니다. 따라서 전체 출력은 1000이 됩니다.

다음으로 또 다른 입력 비트 ‘1’이 D3에 제공되면, 다시 Q3은 1이 되지만, Q3이 D2의 입력으로 제공되므로 이번에는 Q2도 1이 됩니다.

나머지 출력은 여전히 0입니다.

따라서 두 번째 클럭 사이클 이후, 레지스터 내부에 11이 저장되고, 전체 출력은 1100이 됩니다.

비슷하게, 세 번째 입력 비트 ‘1’이 제공되면, 이전 출력 Q2가 D1 입력을 1로 만듭니다.

이로 인해 Q3, Q2, Q1이 모두 1이 되고, Q0은 여전히 0으로 남습니다.

따라서 전체 출력은 1110이 됩니다.

마지막으로, 데이터의 최상위 비트(MSB)를 입력하면 Q1에서의 1이 D0 입력을 논리적 높은 상태로 만듭니다.

따라서 Q0도 1이 됩니다.

이와 같은 방식으로 시프트 레지스터는 ‘1111’을 저장하며, 출력으로 ‘1111’을 표시합니다.

아래는 4비트 SISO 시프트 레지스터 동작 원리를 진리표를 나타낸 것입니다.

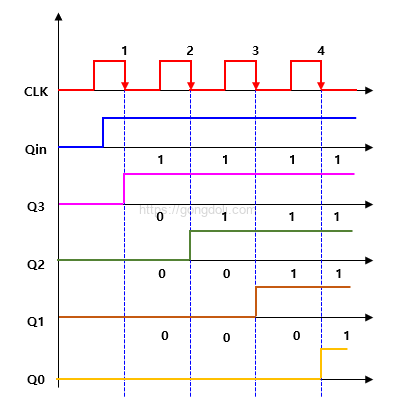

위의 표를 고려하여 SISO 시프트 레지스터의 4비트 데이터 출력 파형을 살펴보겠습니다.

첫 번째는 클럭 입력 신호를 나타내고, 두 번째는 저장될 데이터 입력을 보여줍니다.

이 경우 1111이 데이터로 입력되므로 데이터 입력에서 지속적으로 높은 신호가 나타납니다.

초기에는 모든 출력이 0이었으며, 이는 파형 표현에서 명확히 볼 수 있습니다.

하지만 첫 번째 클럭 펄스가 도착하자 출력 Q3가 0에서 1로 변합니다.

나머지 출력은 여전히 0으로 유지됩니다.

비슷하게, 두 번째 클럭 펄스가 도착하면 Q2가 0에서 1로 변합니다.

이로 인해 Q3과 Q2가 모두 파형에서 논리적 높은 상태를 나타내게 됩니다.

이와 같은 방식으로 위의 그림은 SISO 시프트 레지스터 동작 원리를 명확하게 보여주고 있으며, 4번째 클럭 펄스가 도착하면 4개의 레지스터 출력이 모두 1이 됩니다.

각 클럭 펄스가 도착할 때마다 각 비트가 이동하면서 저장이 이루어지기 때문에 이를 시프트 레지스터라고 부릅니다.

3-2) 직렬 입력 병렬 출력(SIPO) 시프트 레지스터

SIPO 시프트 레지스터는 Serial Input Parallel Output의 약자로, 직렬 입력을 받아 병렬 출력으로 변환해주는 역할을 하는 회로입니다.

이 유형의 시프트 레지스터에서는 데이터가 비트 단위로 직렬 입력되며, 각 클럭 펄스마다 모든 플립플롭(Flip-Flop, FF)의 데이터가 한 자리씩 이동하게 됩니다.

각 플립플롭에서 출력되는 데이터는 병렬로 얻어집니다.

3-2-1) 동작 원리

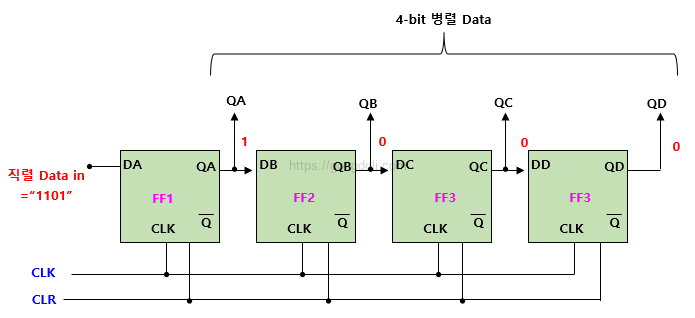

SIPO 시프트 레지스터 동작 원리는 우선 회로는 4개의 D 플립플롭으로 구성되며, 각 플립플롭은 직렬로 연결됩니다.

각 플립플롭은 동일한 클럭 신호를 받아 동작하며, 클리어(CLR) 신호를 추가로 받아 모든 플립플롭의 출력을 초기화할 수 있습니다.

첫 번째 플립플롭의 출력은 두 번째 플립플롭의 입력으로 연결되고, 이 연결이 계속해서 마지막 플립플롭까지 이어집니다.

SIPO 시프트 레지스터는 직렬로 입력된 데이터를 받아 병렬 데이터를 출력합니다.

4비트 SIPO 시프트 레지스터 동작 원리를 예로 들어보겠습니다.

- 초기 상태에서 모든 플립플롭은 클리어 신호로 인해 출력이 0으로 설정됩니다.

즉, QA, QB, QC, QD 모두 논리 0 상태입니다. - 예를 들어, 4비트 데이터 ‘1101’이 입력된다고 가정해 보겠습니다.

첫 번째 클럭 펄스가 발생하면, 첫 번째 플립플롭의 출력 QA는 ‘1’이 되고, 나머지 QB, QC, QD는 여전히 0 상태입니다.

이 시점에서의 출력은 ‘1000’입니다. - 두 번째 클럭 펄스가 발생하면, 첫 번째 플립플롭의 출력 QA는 ‘0’으로 변하고, 나머지 QB, QC, QD 역시 ‘0’이 됩니다.

이 때의 출력은 ‘0100’입니다. - 세 번째 클럭 펄스가 발생하면, 첫 번째 플립플롭의 출력 QA는 ‘1’로, 두 번째 플립플롭의 출력 QB는 ‘0’, 세 번째 플립플롭의 출력 QC는 ‘1’, 마지막으로 네 번째 플립플롭의 출력 QD는 ‘0’이 됩니다. 이 시점에서의 출력은 ‘1011’입니다.

- 마지막으로 네 번째 클럭 펄스가 발생하면, QA는 ‘1’, QB는 ‘1’, QC는 ‘0’, QD는 ‘1’이 됩니다. 이 시점에서의 출력은 ‘1101’입니다.

이처럼 SIPO 시프트 레지스터 동작 원리는 입력된 직렬 데이터를 클럭 펄스에 따라 순차적으로 병렬 출력으로 변환하는 방식으로 동작합니다.

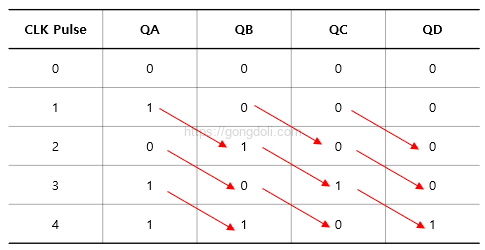

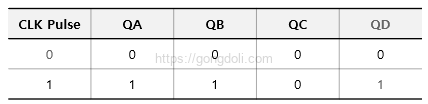

3-2-2) 진리표

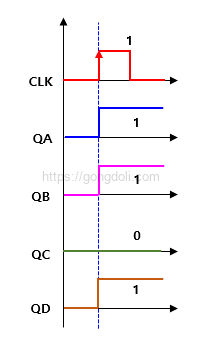

3-2-3) Timing Diagram

여기서는 positive edge 클록 입력 신호를 사용하고 있습니다.

첫 번째 클록 펄스에서 입력 데이터는 QA에 ‘1’로 저장되며, 나머지 QB, QC, QD는 모두 ‘0’이 됩니다.

따라서 출력은 ‘1000’이 됩니다.

두 번째 클록 펄스에서는 출력이 ‘0100’로 변합니다.

세 번째 클록 펄스에서는 출력이 ‘1010’이 되고, 네 번째 클록 펄스에서는 출력이 ‘1101’로 변합니다.

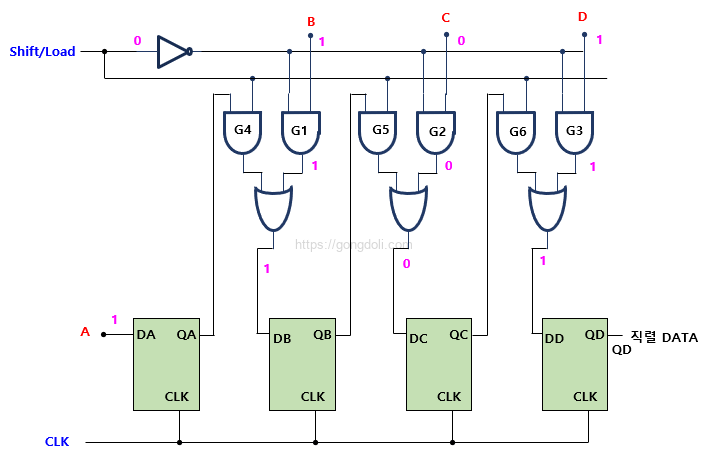

3-3) 병렬 입력, 직렬 출력 (PISO, Parallel-In Serial-Out)

병렬 입력, 직렬 출력(PISO) 시프트 레지스터는 데이터를 병렬로 입력받고, 이를 순차적으로 직렬 출력하는 디지털 회로입니다.

이 회로는 SIPO(Serial-In Parallel-Out) 시프트 레지스터와 반대의 동작 원리를 가지고 있습니다.

PISO 시프트 레지스터에서 각 플립플롭(FF)에는 병렬 데이터가 동시에 입력되고, 이후 클록 신호에 따라 이 데이터가 하나씩 직렬로 출력됩니다.

3-3-1) 동작 원리

PISO 시프트 레지스터 동작 원리를 이해하기 위해, 간단한 예시를 들어보겠습니다.

4비트 데이터 ‘1101’을 병렬로 입력한다고 가정해 보겠습니다.

여기서 각 비트는 각각의 플립플롭에 저장됩니다.

- A = 1 (첫 번째 플립플롭, QA)

- B = 1 (두 번째 플립플롭, QB)

- C = 0 (세 번째 플립플롭, QC)

- D = 1 (네 번째 플립플롭, QD)

이 데이터를 저장한 후, 클록 신호가 적용될 때마다 데이터는 오른쪽으로 한 비트씩 이동하며, 각 비트는 순차적으로 출력됩니다.

- 첫 번째 클록 펄스에서, 가장 오른쪽(QD)의 데이터 ‘1’이 출력됩니다.

- 두 번째 클록 펄스에서는 ‘0’이 출력됩니다(QC의 데이터).

- 세 번째 클록 펄스에서는 ‘1’이 출력됩니다(QB의 데이터).

- 네 번째 클록 펄스에서는 마지막으로 ‘1’이 출력됩니다(QA의 데이터).

3-3-2) 진리표

제어 신호가 ‘1’로 설정되고 클록 펄스 ‘1’이 적용되면 데이터가 시프트되어 QA는 ‘1’, QB는 ‘1’, QC는 ‘0’, QD는 ‘1’이 됩니다.

다음 표와 같이 나타납니다.

- 클록 펄스 ‘2’가 적용되면 데이터가 시프트되어 QA는 ‘0’, QB는 ‘1’, QC는 ‘1’, QD는 ‘0’이 됩니다.

- 클록 펄스 ‘3’이 적용되면 데이터가 시프트되어 QA는 ‘0’, QB는 ‘0’, QC는 ‘1’, QD는 ‘1’이 됩니다.

- 클록 펄스 ‘4’가 적용되면 데이터가 시프트되어 QA는 ‘0’, QB는 ‘0’, QC는 ‘0’, QD는 ‘1’이 됩니다.

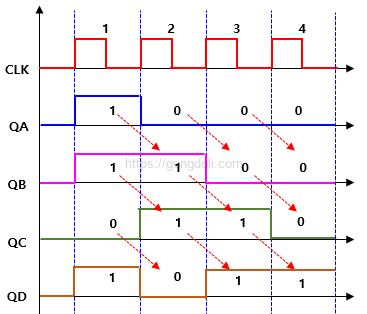

3-3-3) Timing Diagram

3-4) 병렬 입력, 병렬 출력 (PIPO, Parallel-In Parallel-Out)

병렬 입력 병렬 출력 시프트 레지스터(PIPO Shift Register)는 병렬 입력(PI)과 병렬 출력(PO)을 사용하는 시프트 레지스터입니다.

이 레지스터는 클록(CLK) 신호와 함께 작동하며, 병렬 입력 데이터를 병렬 출력으로 제공합니다.

이 유형의 시프트 레지스터는 주로 시간 지연 장치 또는 임시 저장 장치로 사용되며, 이는 CLK 신호의 주파수에 따라 지연 시간이 조정될 수 있습니다.

이 시프트 레지스터는 PA에서 PD까지의 병렬 입력 핀에 데이터를 병렬 형식으로 제공한 후, 동일한 CLK 신호에 의해 각 출력 핀(QA에서 QD)으로 동시에 전송합니다.

단일 CLK 신호가 시프트 레지스터를 로드하고 언로드하는 데 충분합니다.

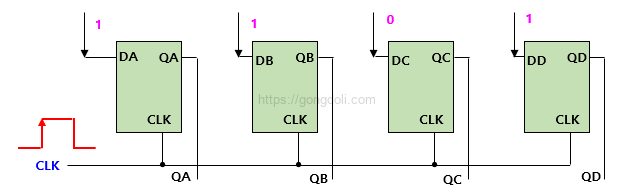

3-4-1) 동작 원리

PIPO 시프트 레지스터 동작 원리는 매우 간단합니다.

이 회로는 4개의 D형 플립플롭(D-FF)으로 구성되어 있으며, 각 플립플롭은 병렬 입력 데이터를 받아들입니다.

예를 들어, DA, DB, DC, DD의 입력 데이터가 각각의 플립플롭에 저장되며, 동일한 클록 신호가 적용됩니다.

이렇게 저장된 데이터는 동시에 병렬 출력됩니다.

이 레지스터는 SISO 시프트 레지스터와 유사하게 임시 저장 장치로 사용되며, 지연 요소로 작동합니다.

병렬 입력 핀(DA에서 D0)에 병렬 형식으로 주어진 데이터는 시프트 레지스터가 클록될 때 각 출력 핀(QA에서 QD)으로 이동합니다.

하나의 CLK 펄스만으로 임시 저장 장치를 로드하고 언로드할 수 있습니다.

위의 회로도는 DA, DB, DC, DD로 표시된 네 개의 입력과 QA, QB, QC, QD로 표시된 플립플롭의 출력을 포함합니다.

모든 D 플립플롭은 동일한 CLK 펄스에 연결됩니다.

입력 데이터가 1101이라고 가정하면, 처음에는 출력이 0000이 됩니다.

첫 번째 CLK 펄스 ‘1’이 적용되면, 입력 데이터가 DA에서 QA로 이동하며 출력은 1101이 됩니다.

3-4-2) 진리표

3-4-3) Timing Diagram

아래에 표시된 것은 PIPO 시프트 레지스터의 타이밍 다이어그램입니다.

여기서는 양의 엣지에서 작동하는 클록 신호를 사용하고 있습니다.

양의 엣지에서 CLK 펄스가 입력될 때 전환이 발생하며, 이때 입력된 데이터가 출력으로 전달됩니다.

따라서 QA는 ‘1’, QB는 ‘1’, QC는 ‘0’, QD는 ‘0’이 되어 이 값이 출력 데이터로 나타나게 됩니다.

I like this blog its a master peace ! Glad I discovered this on google .

Thank you so much! I’m thrilled you think so highly of the blog. Your support truly means a lot!

Hi there, I found your site by means of Google at the same time as looking for a similar subject, your site came up, it seems to be great. I have bookmarked it in my google bookmarks.

Thank you for your kind words! I’m glad you found my site and bookmarked it

Someone essentially help to make seriously articles I would state. This is the very first time I frequented your web page and thus far? I amazed with the research you made to make this particular publish extraordinary. Magnificent job!

Thank you so much for the wonderful feedback!

I’m truly glad the effort behind this post stood out to you

Hello there, You’ve done an excellent job. I’ll certainly digg it and personally recommend to my friends. I am sure they’ll be benefited from this site.

hank you so much for your kind words and support!

It means a lot to know that you found value here and are willing to share it with others.

I truly hope your friends benefit from it as well.

You should take part in a contest for one of the best blogs on the web. I will recommend this site!

That means a lot—thanks for the support!

Its like you learn my mind! You appear to know a lot about this, like you wrote the ebook in it or something. I think that you can do with a few to force the message house a little bit, but other than that, this is great blog. An excellent read. I’ll definitely be back.

I appreciate your encouraging words.

Excellent blog here! Also your web site loads up fast! What web host are you using? Can I get your affiliate link to your host? I wish my site loaded up as fast as yours lol

Thank you for your kind words

wonderful post.Ne’er knew this, appreciate it for letting me know.

I’m glad it was helpful

Im no longer positive where you are getting your info, but great topic. I needs to spend a while learning much more or understanding more. Thanks for great information I used to be in search of this information for my mission.

Thank you for your kind words. I’m glad the information was helpful for your mission.