1. 이진 감산기 회로 설계란?

1-1) 이진 감산기의 정의와 기본 개념

이진 감산기(Binary Subtractor)는 두 개의 이진수를 빼기 위해 사용되는 디지털 회로입니다.

기본적으로 이진 감산기는 입력으로 두 개의 이진수와 빌림(Borrow) 신호를 받아, 그 차이(Difference)와 새로운 빌림 출력을 생성합니다.

이진 감산기 회로 설계는 이러한 기능을 구현하기 위해 논리 게이트를 사용하여 구성됩니다.

1-2) 이진 감산기의 주요 기능과 역할

이진 감산기의 주요 기능은 두 개의 이진수를 비교하여 그 차이를 계산하는 것입니다.

이진 감산기 회로 설계에서는 다음과 같은 역할이 강조됩니다.

- 차이 계산 : 두 이진수의 차이를 계산하여 출력합니다.

- 빌림 처리 : 빌림 신호를 처리하여 다음 비트로 전파합니다.

- 논리 연산 수행 : XOR, AND, NOT 등의 논리 게이트를 사용하여 감산 연산을 수행합니다.

1-3) 이진 감산기의 응용 분야

이진 감산기 회로 설계는 다양한 디지털 시스템에서 중요한 역할을 합니다.

- 컴퓨터 프로세서 : 연산 기능을 수행하기 위해 사용됩니다.

- 디지털 신호 처리 : 신호 간의 차이를 계산하여 데이터 처리를 수행합니다.

- 제어 시스템 : 상태 변수 간의 차이를 계산하여 제어 로직을 구현합니다.

- 계산기 : 기본적인 산술 연산 기능을 제공합니다.

이진 감산기 회로 설계는 컴퓨터의 기본 연산 단위로서 매우 중요하며, 정확한 연산을 위해 정밀하게 설계되어야 합니다.

이를 통해 컴퓨터와 다양한 디지털 시스템에서 효율적이고 정확한 연산을 수행할 수 있습니다.

- 연관 참조 : 비교기 회로 설계, 유형, 회로 설계 방법, 예제, 주의 사항 7가지

- 연관 참조 : 이진 가산기 회로 설계, 회로 설계 방법, 예제 설계 2가지

- 연관 참조 : 2진 디코더 회로 설계, 회로 설계 방법, 예제,설계 문제 4가지

- 연관 참조 : Encoder 회로 설계, 회로 설계 방법, 예제, 흔한 설계 문제 4가지

- 연관 참조 : Demultiplexer 회로 설계, 회로 설계 방법, 예제, 흔한 설계 문제 5가지

- 연관 참조 : Multiplexer 회로 설계,유형과 종류,회로 설계 방법, 예제

- 연관 참조 : 조합 논리 회로, 회로 설계, 부울 대수 이용, 카르노 맵 이용,예제1

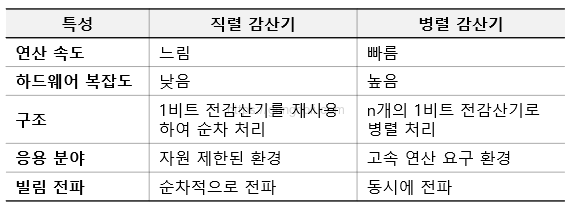

2. 이진 직렬 감산기와 병렬 감산기

이진 감산기 회로 설계는 두 개의 이진수를 감산하는 디지털 회로입니다.

이진 감산기는 직렬 감산기와 병렬 감산기로 나눌 수 있으며, 각 방법은 다른 하드웨어 구조와 연산 속도를 갖습니다.

이 두 감산기의 차이점을 이해하기 위해 각 방식의 설계와 특성을 비교 설명하겠습니다.

2-1) 직렬 감산기 (Serial Subtractor)

직렬 감산기는 각 비트를 순차적으로 처리하여 감산 연산을 수행하는 구조입니다.

한 비트의 연산이 완료된 후에 다음 비트의 연산이 시작되므로, 전체 연산이 직렬로 진행됩니다.

2-1-1) 특성 및 동작

- 연산 속도

느림 : 각 비트의 연산이 순차적으로 진행되기 때문에 전체 연산 시간이 길어집니다.

이전 비트의 빌림(Borrow)이 다음 비트의 연산에 사용되므로, 빌림 전파 시간이 전체 연산 속도를 결정합니다. - 하드웨어 복잡도

낮음 : 회로가 간단하여 적은 하드웨어 자원으로 구현할 수 있습니다.

보통 하나의 1비트 전감산기를 사용하여 비트를 하나씩 처리합니다. - 구조

하나의 1비트 전감산기를 사용하여 순차적으로 연산을 수행합니다.

각 단계의 빌림 출력이 다음 단계의 빌림 입력으로 사용됩니다. - 응용

하드웨어 자원이 제한된 경우에 유리합니다.

연산 속도가 중요하지 않은 경우에 사용됩니다.

2-1-2) 직렬 감산기 구성 예

- 입력 : 두 개의 n비트 이진 숫자 A와 B, 초기 빌림 입력(Bin).

- 출력 : n비트 차이 결과와 최종 빌림 출력(Bout).

각 비트에 대해 다음의 연산이 이루어집니다.

- 차이 비트 (D) = A⊕B⊕Bin

- 빌림 비트 (Bout) = (A’⋅B)+((A⊕B)⋅Bin)

2-2) 병렬 감산기 (Parallel Subtractor)

병렬 감산기는 모든 비트를 동시에 처리하여 감산 연산을 수행하는 구조입니다.

각 비트의 연산이 병렬로 진행되므로, 연산 속도가 빠릅니다.

2-2-1) 특성 및 동작

- 연산 속도

빠름 : 모든 비트를 동시에 처리할 수 있어 전체 연산 시간이 1비트 연산 시간과 유사합니다.

빌림 전파가 필요하지만, 병렬 처리를 통해 빠른 속도를 유지할 수 있습니다. - 하드웨어 복잡도

높음 : 각 비트에 대해 별도의 전감산기가 필요하므로 하드웨어 자원이 많이 요구됩니다. - 구조

n개의 1비트 전감산기가 병렬로 연결되어 각 비트를 동시에 처리합니다. - 응용

고속 연산이 필요한 경우에 적합합니다.

계산 속도가 중요한 디지털 시스템에서 사용됩니다.

2-2-2) 병렬 감산기 구성 예

- 입력: 두 개의 n비트 이진 숫자 A와 B, 초기 빌림 입력(Bin).

- 출력: n비트 차이 결과와 최종 빌림 출력(Bout).

각 비트에 대해 다음의 연산이 이루어집니다.

- 차이 비트 (D) = A⊕B⊕Bin

- 빌림 비트 (Bout) = (A’⋅B)+((A⊕B)⋅Bin)

2-3) 직렬 감산기와 병렬 감산기의 비교

- 직렬 감산기는 하드웨어 리소스가 제한된 상황에서 유용하며, 낮은 연산 속도가 허용되는 경우에 사용됩니다.

- 병렬 감산기는 고속 연산이 필요한 응용 분야에 적합하며, 복잡한 하드웨어 구조를 감당할 수 있는 환경에서 사용됩니다.

이러한 특성들을 고려하여 설계 요구사항에 맞는 감산기 구조를 선택하는 것이 중요합니다.

2. 이진 감산기 회로 설계 예제

2-1) 1비트 반감산기 회로 설계 단계별 설명

1비트 반감산기(Half Subtractor)는 두 개의 입력 비트를 받아 차이와 빌림 출력을 생성하는 기본적인 디지털 회로입니다.

이진 감산기 회로 설계의 첫 단계로 반감산기를 설계합니다.

2-1-1) 입력 및 출력 정의

- 입력: A (피감수), B (감수)

- 출력: D (차이), Bout (빌림)

2-1-2) 진리표 작성

2-1-3) 논리식 도출

- 차이(D): A XOR B

- 빌림(Bout): NOT A AND B

2-1-4) 회로 구현

XOR 게이트를 사용하여 A와 B의 차이를 계산

AND 게이트와 NOT 게이트를 사용하여 빌림을 계산

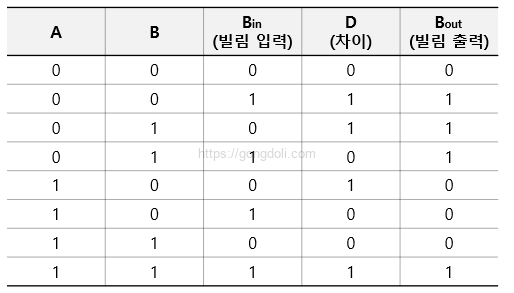

2-2) 1비트 전감산기 진리표와 회로 구현

1비트 전감산기(Full Subtractor)는 두 개의 입력 비트와 하나의 빌림 입력을 받아 차이와 빌림 출력을 생성하는 회로입니다.

이진 감산기 회로 설계에서 전감산기는 반감산기보다 더 복잡한 연산을 처리합니다.

2-2-1) 진리표 작성

2-2-2) 논리식 도출

- 차이(D): (A XOR B) XOR Bin

- 빌림(Bout): (NOT A AND B) OR ((A XOR B) AND Bin)

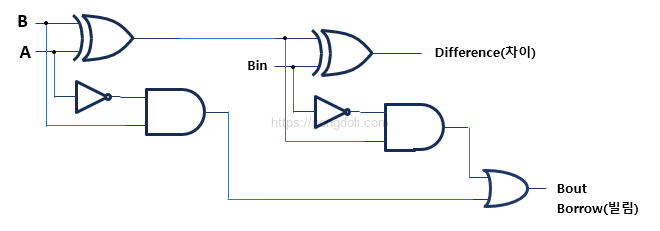

2-2-3) 회로 구현

XOR 게이트 두 개를 직렬로 연결하여 차이 계산

AND 게이트와 OR 게이트를 조합하여 빌림 계산

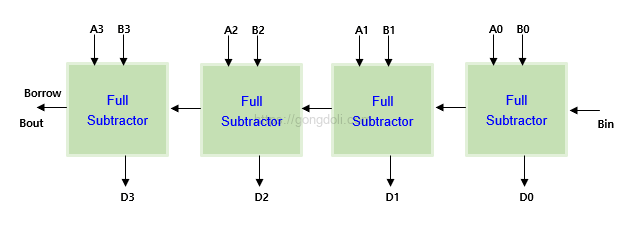

2-3) 4비트 직렬 감산기 회로 설계

4비트 직렬 이진 감산기 회로 설계는 두 4비트 이진 숫자를 순차적으로 감산하는 프로세스를 포함합니다.

직렬 감산기는 각 비트 위치에서 계산을 수행하여 다음 비트로 빌림을 전파하는 방식으로 동작합니다.

이 방식은 병렬 감산기에 비해 하드웨어가 간단하지만, 연산 속도는 더 느릴 수 있습니다.

4비트 직렬 감산기는 두 개의 4비트 이진 숫자 A와 B를 입력으로 받아, A – B를 계산하여 4비트 결과와 최종 빌림을 출력합니다.

2-3-1) 구성 요소

- 1비트 전감산기 (Full Subtractor)

기본 구성 블록으로 각 비트의 차이를 계산하고, 다음 비트로 빌림을 전파하는 역할을 합니다. - 4비트 레지스터

두 4비트 입력(A와 B)을 저장하는 레지스터입니다.

A와 B는 각각 직렬로 전송되어 전감산기에 입력됩니다. - 플립플롭 (Flip-Flop)

각 단계의 빌림을 저장하고 다음 단계로 전달합니다.

초기 빌림은 Bin이며, 최종 빌림 출력은 Bout입니다. - 클럭 신호 (Clock Signal)

비트별 연산을 제어하여 각 단계의 연산이 클럭 신호에 맞춰 순차적으로 진행되도록 합니다.

2-3-2) 1비트 전감산기 설계

이진 감산기 회로 설계에서 1비트 전감산기는 다음과 같은 연산을 수행합니다.

- 차이 비트 (D) = A⊕B⊕Bin

- 빌림 비트 (Bout) = (A’⋅B)+((A⊕B)⋅Bin)

각 비트에 대해 이 연산을 수행하여 차이 비트와 빌림 비트를 계산합니다.

2-3-3) 4비트 직렬 감산기 회로 구성

이진 감산기 회로 설계에서 4비트 직렬 감산기 회로는 다음과 같이 구성됩니다.

- 입력: 두 4비트 숫자 A와 B, 초기 빌림 입력Bin

- 출력: 4비트 차이 결과와 최종 빌림 출력Bout.

- 각 비트의 연산은 클럭 신호에 맞춰 순차적으로 진행됩니다.

- 각 1비트 전감산기는 이전 단계의 빌림을 입력으로 받아 계산합니다.

회로 설명

- 1단계: 첫 번째 비트 A0와 B0가 1비트 전감산기에 입력됩니다.

초기 빌림 입력은 Bin=0입니다. - 2단계: 두 번째 비트 A1와 B1가 전감산기에 입력됩니다.

이전 단계의 빌림 출력이 현재 단계의 빌림 입력으로 사용됩니다. - 3단계: 세 번째 비트 A2와 B2가 전감산기에 입력됩니다.

이전 단계의 빌림 출력이 현재 단계의 빌림 입력으로 사용됩니다. - 4단계: 네 번째 비트 A3와 B3가 전감산기에 입력됩니다.

이전 단계의 빌림 출력이 현재 단계의 빌림 입력으로 사용됩니다.

동작 원리

- 각 클럭 사이클에서 한 비트의 감산 연산이 수행되며, 그 결과가 차이 비트와 빌림 비트로 출력됩니다.

- 모든 비트에 대해 연산이 완료되면, 최종 차이 결과가 출력되며, 최종 빌림 출력은 최종 결과의 부호를 나타냅니다.

예를 들어, 입력이 A = 1101 (13), B = 0110 (6)일 때, 설명을 해보겠습니다.

- 1단계 (A0, B0): 1 – 0 = 1, Bout=0

- 2단계 (A1, B1): 0 – 1 = 1 (빌림), Bout=1

- 3단계 (A2, B2): 1 – 1 (빌림) = 1, Bout=0

- 4단계 (A3, B3): 1 – 0 = 1, Bout=0

결과는 차이(D) = 0111 (7), 최종 빌림 출력 Bout=0

4비트 직렬 이진 감산기 회로 설계는 각 비트를 순차적으로 연산하여 빌림을 전파하는 구조로, 하드웨어 복잡도가 낮고 설계가 단순합니다.

하지만, 각 비트를 순차적으로 연산하기 때문에 병렬 감산기에 비해 연산 속도가 느릴 수 있습니다.

이 설계 방식은 하드웨어 자원이 제한적이지만, 고속 연산이 필요하지 않은 경우에 적합합니다.

I appreciate, cause I found exactly what I was looking for. You have ended my four day long hunt! God Bless you man. Have a great day. Bye

Thank you so much! I’m glad I could help end your search. Wishing you a wonderful day ahead!

whoah this blog is excellent i love reading your posts. Keep up the great work! You know, lots of people are looking around for this information, you could aid them greatly.

Thank you so much for such an encouraging message.

I’m really happy to hear the posts are meaningful for you.

There is obviously a bunch to know about this. I believe you made various nice points in features also.

Thanks so much!

I’m glad you found the topic interesting and appreciated the points I made about the features.

I enjoy your writing style really enjoying this web site.

Thank you so much!

I’m really glad you’re enjoying both the writing and the site.

Today, I went to the beach front with my children. I found a sea shell and gave it to my 4 year old daughter and said “You can hear the ocean if you put this to your ear.” She placed the shell to her ear and screamed. There was a hermit crab inside and it pinched her ear. She never wants to go back! LoL I know this is totally off topic but I had to tell someone!

-_-;

Great post, you have pointed out some good points, I as well think this s a very good website.

Thank you so much for your kind words!

I’m really glad you found the post insightful and the website valuable.

Some truly great info , Glad I found this. “Underpromise overdeliver.” by Tom Peters.

Wise words—thanks for sharing!

You are a very intelligent person!

Thank you, that means a lot.

Thankyou for this wonderful post, I am glad I found this web site on yahoo.

I truly appreciate your kind words, and I’m glad you discovered the site.

You are a very clever individual!

Thank you kindly for your generous compliment.