1. 개요

1-1) 2진 디코더의 정의와 기본 개념

2진 디코더 회로 설계는 이진수 입력을 받아 특정 출력을 활성화시키는 조합 논리 회로입니다.

즉, 이진 입력을 받아 그에 상응하는 출력 신호를 생성하는 장치입니다.

예를 들어, 2개의 입력을 가진 2진 디코더는 4개의 출력을 가지며, 각 입력 조합에 따라 하나의 출력만이 활성화됩니다.

기본적으로, 2진 디코더는 다음과 같은 형식으로 동작합니다.

- 입력 : n개의 이진 입력 비트

- 출력 : 2n개의 출력 라인

2진 디코더는 주로 디지털 회로에서 주소 디코딩, 메모리 셀 선택, 데이터 분배 등의 역할을 수행합니다.

1-2) 2진 디코더의 주요 기능과 역할

2진 디코더 회로 설계의 주요 기능과 역할은 다음과 같습니다.

- 주소 디코딩: CPU가 메모리나 I/O 장치를 접근할 때 사용됩니다.

특정 주소에 해당하는 메모리 셀이나 I/O 포트를 활성화하는 데 사용됩니다. - 데이터 분배: 멀티플렉서와 함께 사용되어 데이터를 여러 목적지로 분배하는 데 사용됩니다.

- 명령어 디코딩: 프로세서에서 명령어를 해석하여 해당하는 제어 신호를 생성하는 데 사용됩니다.

- 신호 라우팅: 특정 신호를 여러 경로로 분배하여 필요한 곳에 전달하는 데 사용됩니다.

예를 들어, 2-to-4 디코더의 경우, 2개의 입력 비트를 받아 4개의 출력 중 하나를 활성화합니다.

입력이 00이면 출력 0이 활성화되고, 입력이 01이면 출력 1이 활성화되는 식입니다.

1-3) 2진 디코더와 Encoder의 차이점

2진 디코더와 Encoder는 서로 반대의 역할을 하는 디지털 회로입니다.

그 차이점을 이해하는 것이 중요합니다.

2진 디코더 회로 설계는 이진 입력을 받아 특정 출력을 활성화하는 반면, Encoder 회로 설계는 여러 입력 신호 중 하나를 선택하여 이진 형태의 출력을 생성합니다.

즉, 디코더는 주어진 이진 입력을 사용하여 여러 출력 중 하나를 선택하는 반면, Encoder는 여러 입력 중 하나를 선택하여 이진 형태의 출력을 생성하는 역할을 합니다.

- 연관 참조 : 이진 감산기 회로 설계, 직렬과 병렬 감산기 비교, 회로 설계 예제 3가지

- 연관 참조 : 비교기 회로 설계, 유형, 회로 설계 방법, 예제, 주의 사항 7가지

- 연관 참조 : 이진 가산기 회로 설계, 회로 설계 방법, 예제 설계 2가지

- 연관 참조 : Encoder 회로 설계, 회로 설계 방법, 예제, 흔한 설계 문제 4가지

- 연관 참조 : Demultiplexer 회로 설계, 회로 설계 방법, 예제, 흔한 설계 문제 5가지

- 연관 참조 : Multiplexer 회로 설계,유형과 종류,회로 설계 방법, 예제

- 연관 참조 : 조합 논리 회로, 회로 설계, 부울 대수 이용, 카르노 맵 이용,예제1

2. 2진 디코더 회로 설계 방법

2-1) 기본 설계 원리: 진리표에서 논리식으로

2진 디코더 회로 설계는 주어진 입력에 따라 출력이 결정되는 논리 회로를 구성하는 과정입니다.

이 과정은 진리표를 작성하고, 이를 기반으로 논리식을 도출하는 순서로 진행됩니다.

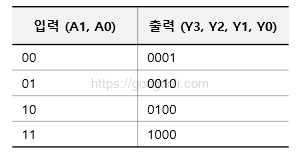

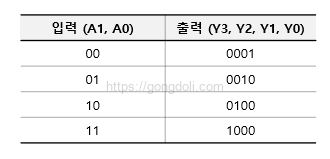

- 진리표 작성

입력 비트에 따른 모든 가능한 출력 조합을 나열합니다.

예를 들어, 2-to-4 디코더의 경우 2개의 입력이 있으므로 총 4개의 출력 조합이 존재합니다.

- 논리식 도출

진리표를 기반으로 각 출력에 대한 논리식을 도출합니다.

여기서 각 출력은 AND, OR, NOT 게이트를 조합하여 표현됩니다.

예를 들어, Y0는 입력 A1과 A0이 모두 0일 때만 1이 되므로, Y0 = A1′ A0’입니다.

2-2) 2진 디코더의 논리식 도출 과정

2진 디코더 회로 설계의 진리표에서 논리식을 도출하는 과정은 다음과 같습니다.

- 진리표 분석 : 각 출력이 1이 되는 입력 조합을 확인합니다.

- 논리식 구성 : 각 출력에 대해 AND 게이트를 사용하여 필요한 입력 조합을 만듭니다.

그런 다음, 이를 OR 게이트로 조합하여 최종 출력을 만듭니다.

예를 들어, 2-to-4 디코더의 경우

- Y0 = A1′ A0′

- Y1 = A1′ A0

- Y2 = A1 A0′

- Y3 = A1 A0

2-3) 선택 신호를 이용한 회로 구성 방법

2진 디코더 회로 설계에서 선택 신호는 입력 비트를 의미합니다.

선택 신호는 디코더의 출력 중 하나를 활성화시키는 역할을 합니다.

선택 신호를 이용한 회로 구성 방법은 다음과 같습니다.

- 입력 비트 설정 : 디코더의 입력 비트를 선택 신호로 사용합니다.

- 논리 게이트 배치 : 진리표에서 도출한 논리식을 바탕으로 AND, OR, NOT 게이트를 배치합니다.

- 회로 연결 : 각 출력에 해당하는 논리 게이트를 올바르게 연결하여 입력에 따른 출력이 정확히 나오도록 합니다.

2-4) 2진 디코더 회로의 최적화 기법

2진 디코더 회로 설계에서 최적화는 회로의 효율성을 높이는 것을 목표로 합니다.

최적화 기법은 다음과 같습니다.

- 게이트 최소화 : 사용되는 논리 게이트의 수를 최소화하여 회로의 복잡성을 줄입니다.

카르노 맵(Karnaugh Map)을 사용하여 간소화할 수 있습니다. - 전력 소모 줄이기 : 불필요한 게이트를 제거하고, 저전력 논리 소자를 사용하여 전력 소모를 줄입니다.

- 속도 향상 : 신호 전파 지연을 최소화하기 위해 게이트 수를 줄이고, 고속 논리 소자를 사용합니다.

예를 들어, 2-to-4 디코더의 경우, 각 출력에 필요한 AND 게이트와 NOT 게이트의 수를 최소화하여 최적의 설계를 도출할 수 있습니다.

3. 2진 디코더 회로 설계 예제

3-1) 2-to-4 디코더 회로 설계 단계별 설명

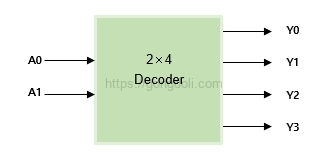

2-to-4 디코더 회로 설계는 2개의 입력 비트를 받아 4개의 출력을 생성하는 과정입니다.

이 과정을 단계별로 설명하면 다음과 같습니다.

3-1-1) 진리표 작성

입력과 출력의 관계를 나타내는 진리표를 작성합니다.

3-1-2) 논리식 도출

각 출력에 대한 논리식을 도출합니다.

- Y0 = A1′ A0′

- Y1 = A1′ A0

- Y2 = A1 A0′

- Y3 = A1 A0

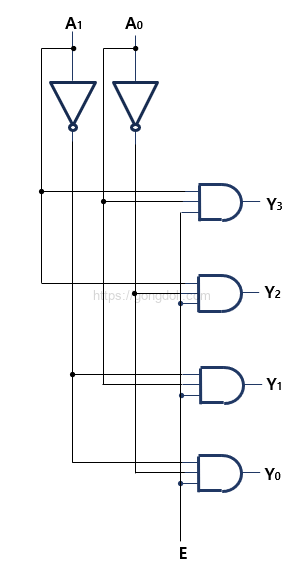

3-1-3) 회로 구성

도출된 논리식을 바탕으로 회로를 구성합니다.

AND, NOT 게이트를 사용하여 입력을 원하는 형태로 결합합니다.

- Y0: A1과 A0의 NOT 게이트 출력 값을 AND 게이트에 입력합니다.

- Y1: A1의 NOT 게이트 출력과 A0 값을 AND 게이트에 입력합니다.

- Y2: A1 값과 A0의 NOT 게이트 출력 값을 AND 게이트에 입력합니다.

- Y3: A1과 A0 값을 AND 게이트에 입력합니다.

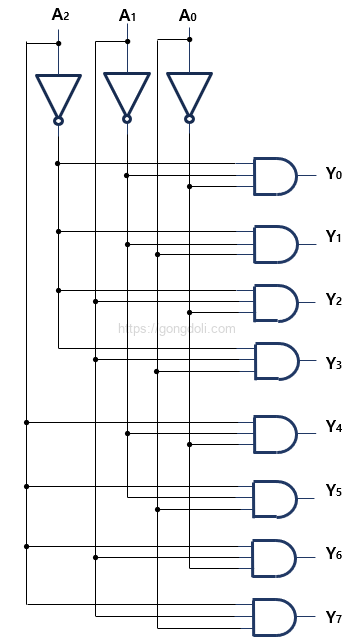

3-2) 3-to-8 디코더의 진리표와 회로 구현

3-to-8 디코더는 3개의 입력 비트를 받아 8개의 출력을 생성합니다.

다음은 그 진리표와 회로 구현 방법입니다.

3-2-1) 진리표 작성

3-2-2) 논리식 도출

각 출력에 대한 논리식을 도출합니다.

- Y0 = A2′ A1′ A0′

- Y1 = A2′ A1′ A0

- Y2 = A2′ A1 A0′

- Y3 = A2′ A1 A0

- Y4 = A2 A1′ A0′

- Y5 = A2 A1′ A0

- Y6 = A2 A1 A0′

- Y7 = A2 A1 A0

3-2-3) 회로 구성

예를 들어, Y0는 A2, A1, A0의 NOT 게이트 출력을 입력으로 받는 AND 게이트로 구성됩니다.

각 출력에 대해 동일한 방식으로 회로를 구성하면 됩니다.

3-3) 2진 디코더를 활용한 실제 응용 예제

2진 디코더 회로 설계는 다양한 실제 응용에서 중요한 역할을 합니다.

몇 가지 예를 들면

- 메모리 주소 디코딩

CPU가 메모리에 접근할 때, 특정 주소를 지정하여 해당 메모리 셀을 활성화하는 데 사용됩니다.

예를 들어, 2-to-4 디코더를 사용하여 4개의 메모리 셀 중 하나를 선택할 수 있습니다. - 데이터 분배

멀티플렉서와 함께 사용되어 데이터를 여러 목적지로 분배하는 데 사용됩니다.

예를 들어, 네트워크에서 데이터 패킷을 특정 경로로 라우팅하는 데 사용될 수 있습니다. - 명령어 디코딩

프로세서에서 명령어를 해석하여 해당하는 제어 신호를 생성하는 데 사용됩니다.

예를 들어, 특정 연산을 수행하기 위해 ALU의 제어 신호를 생성할 수 있습니다.

4. 2진 디코더 회로 설계 문제와 해결 방법

4-1) 신호 충돌 문제

문제 설명

2진 디코더 회로 설계에서 신호 충돌 문제는 두 개 이상의 출력이 동시에 활성화되는 경우 발생할 수 있습니다.

이는 잘못된 회로 설계나 부적절한 입력 타이밍으로 인해 발생할 수 있습니다

해결 방법

- 신호 무결성 검증 : 회로 설계 단계에서 신호 충돌 가능성을 사전에 검토하고 검증합니다.

- 타이밍 조정 : 입력 신호의 타이밍을 조정하여 동일한 시간에 두 개 이상의 출력이 활성화되지 않도록 합니다.

- 전송선로 이론 : 신호 전달 경로에서 발생하는 반사 및 왜곡을 최소화하기 위해 전송선로 이론을 적용하여 적절한 종단 저항을 사용합니다.

4-2) 입력 신호의 타이밍 문제

문제 설명

입력 신호의 타이밍 문제는 신호가 올바르게 전파되지 않아 예상치 못한 출력이 발생하는 경우를 의미합니다.

이는 신호 전파 지연, 클록 신호의 부정확성 등으로 인해 발생할 수 있습니다.

해결 방법

- 동기화 회로 : 클록 신호를 사용하여 입력 신호를 동기화함으로써 신호 전파 지연 문제를 해결할 수 있습니다.

- 타이밍 분석 : 회로의 각 단계에서 발생하는 지연 시간을 분석하고 필요한 경우 추가 버퍼를 사용하여 타이밍을 조정합니다.

- 게이트 지연 최소화 : 고속 논리 게이트를 사용하여 신호 전파 지연을 최소화합니다.

4-3) 잡음 민감도 문제

문제 설명

잡음 민감도 문제는 외부 잡음이나 전자기 간섭(EMI)에 의해 회로의 성능이 저하되는 경우를 말합니다.

이는 잘못된 신호 해석이나 불필요한 출력 활성화를 초래할 수 있습니다.

해결 방법

- 차폐 및 접지 : 회로를 적절히 차폐하고 접지하여 외부 잡음을 차단합니다.

- 디커플링 커패시터 : 전원 공급 라인에 디커플링 커패시터를 추가하여 전원 잡음을 최소화합니다.

- 잡음 필터링 : 입력 신호에 잡음 필터링 회로를 추가하여 잡음의 영향을 줄입니다.

4-4) 전력 소모 문제

문제 설명

2진 디코더 회로 설계에서 전력 소모 문제는 회로의 비효율적인 설계로 인해 발생할 수 있습니다.

이는 과도한 전력 소모로 인해 시스템 전체의 효율성이 떨어지는 문제를 일으킬 수 있습니다.

해결 방법

- 전력 최적화 설계 : 저전력 논리 게이트를 사용하고, 회로 설계 시 전력 최적화를 고려합니다.

- 전력 관리 기법 : 필요하지 않은 경우 출력 신호를 비 활성화하는 전력 관리 기법을 적용합니다.

- 시뮬레이션 및 분석 : 설계 단계에서 전력 소모를 시뮬레이션하고 분석하여 최적의 전력 소비를 유지합니다.

There may be noticeably a bundle to learn about this. I assume you made certain nice factors in features also.

Thank you for your thoughtful observation! I’m glad you noticed the key points and found them valuable

I got good info from your blog

Thank you so much

I simply couldn’t depart your web site before suggesting that I actually enjoyed the standard info a person provide for your guests? Is gonna be again incessantly in order to investigate cross-check new posts

Thank you so much for your kind words!

We’re truly glad to hear that you found the information helpful and enjoyable.

You’re always welcome back anytime, and we’ll keep sharing fresh and valuable content for you to explore.

Looking forward to having you visit again soon!

I’ve been browsing online greater than 3 hours these days, yet I by no means discovered any interesting article like yours. It¦s pretty worth sufficient for me. Personally, if all site owners and bloggers made just right content as you probably did, the net can be a lot more helpful than ever before.

Wow, thank you so much for your kind words!

It truly means a lot to know that my content stood out to you.

I have been exploring for a bit for any high quality articles or blog posts on this kind of house . Exploring in Yahoo I finally stumbled upon this site. Studying this information So i am satisfied to express that I have a very good uncanny feeling I discovered just what I needed. I most for sure will make sure to don¦t forget this site and provides it a glance on a continuing basis.

Thank you so much for your thoughtful message!

I’m truly glad you found exactly what you were looking for.

It means a lot to know this site made a difference for you.

You’re always welcome back anytime!

I haven?¦t checked in here for a while as I thought it was getting boring, but the last several posts are good quality so I guess I will add you back to my everyday bloglist. You deserve it my friend 🙂

That truly means a lot—thank you!

I’m glad the recent posts caught your attention again.

I get pleasure from, lead to I discovered just what I used to be having a look for. You’ve ended my 4 day lengthy hunt! God Bless you man. Have a great day. Bye

That’s truly heartwarming to hear—thank you!

I’m so glad you found exactly what you were searching for after such a long hunt.

Unquestionably believe that which you stated. Your favorite reason seemed to be on the internet the easiest thing to be aware of. I say to you, I certainly get irked while people think about worries that they plainly don’t know about. You managed to hit the nail upon the top and also defined out the whole thing without having side effect , people could take a signal. Will likely be back to get more. Thanks

Really grateful—hope to see you back soon!

My brother recommended I might like this web site. He was totally right. This post truly made my day. You can not imagine simply how much time I had spent for this information! Thanks!

That means a lot—thanks for sharing!

I’m so glad it helped.

Merely a smiling visitant here to share the love (:, btw outstanding pattern. “Individuals may form communities, but it is institutions alone that can create a nation.” by Benjamin Disraeli.

Thanks for the kind visit—and great quote!

I got what you intend, thankyou for putting up.Woh I am glad to find this website through google.

Thank you for your kind words.

This web site is really a walk-through for all of the info you wanted about this and didn’t know who to ask. Glimpse here, and you’ll definitely discover it.

Thank you so much for your thoughtful comment. I’m glad the site was able to provide the information you were looking for.

You made some clear points there. I did a search on the subject and found most people will consent with your blog.

Thank you for taking the time to look into the topic. I’m glad to hear that others also find the points convincing and that the blog resonates with you.

There’s noticeably a bundle to know about this. I assume you made sure good factors in options also.

Thank you for your kind words.

I would like to thnkx for the efforts you have put in writing this blog. I am hoping the same high-grade blog post from you in the upcoming as well. In fact your creative writing abilities has inspired me to get my own blog now. Really the blogging is spreading its wings quickly. Your write up is a good example of it.

Thank you for your encouraging words. I’m glad my writing inspired you

Perfect piece of work you have done, this site is really cool with superb information.

Thank you very much for your kind words.

I’m glad you find the site useful.

I appreciate your support and hope to see you again!