1. AND 게이트란 무엇인가?

디지털 전자 회로 설계에서, 논리 게이트는 기본적인 빌딩 블록입니다.

이 중 AND 게이트는 가장 단순하면서도 중요한 논리 게이트 중 하나로, 여러 디지털 시스템에서 핵심적인 역할을 합니다.

AND 게이트 회로는 입력 신호들이 모두 참(True)일 때에만 출력이 참(True)이 되는 논리적 연산을 수행합니다.

이를 통해 다양한 논리적 결정을 내리고, 복잡한 회로를 구축하는 데 사용됩니다.

1-1) AND 게이트의 정의

AND 게이트는 “모두 참이어야 한다”는 의미를 갖는 논리적 연산을 수행하는 디지털 논리 회로입니다.

AND 게이트 회로는 보통 두 개 이상의 입력을 가지며, 이 모든 입력이 논리적 ‘1’ (HIGH)일 때에만 출력이 논리적 ‘1’이 됩니다.

반대로, 하나라도 입력이 논리적 ‘0’ (LOW)일 경우, 출력은 항상 논리적 ‘0’이 됩니다.

이러한 동작을 이해하기 쉽게 진리표로 나타낼 수 있습니다.

다음은 가장 기본적인 2 입력 AND 게이트의 진리표입니다.

진리표를 보면, 두 입력이 모두 1일 때만 출력이 1이 됨을 알 수 있습니다.

이처럼, AND 게이트는 모든 입력이 참일 때에만 출력을 참으로 만드는 논리적 AND 연산을 수행합니다.

1-2) AND 게이트 회로의 기본 원리

AND 게이트 회로는 입력 신호들이 모두 활성화 되었을 때, 즉 HIGH 상태일 때만 출력을 활성화하는 방식으로 동작합니다.

이 원리는 일반적인 전기 스위치의 작동 방식과 유사합니다.

예를 들어, 두 개의 스위치가 모두 켜져 있어야 전구가 켜지는 것과 같습니다.

이 두 스위치가 AND 게이트의 두 입력에 해당하며, 전구가 켜지는 상태가 AND 게이트의 출력입니다.

AND 게이트의 기본 원리는 다음과 같이 설명할 수 있습니다.

모든 입력의 논리적 곱: AND 게이트의 출력은 입력 신호들의 논리적 곱(product)입니다.

이는 모든 입력이 1일 때에만 출력이 1이 된다는 의미입니다.

이를 논리식으로 표현하면 다음과 같습니다: Q = A ⋅ B (여기서 ‘⋅’는 논리적 AND 연산을 의미합니다).

전기적 동작: 실제 회로에서, AND 게이트는 트랜지스터나 다이오드를 사용하여 구현됩니다.

입력 전압이 특정 임계값 이상일 때, 출력 전압이 HIGH가 되도록 설계됩니다.

아래는 기본적인 2입력 AND 게이트 회로의 전기적 동작을 간단히 설명한 것입니다.

- 다이오드 기반 AND 게이트: 두 개의 다이오드가 병렬로 연결되어 입력 신호가 모두 HIGH일 때만 전류가 흐르게 되어 출력이 HIGH가 됩니다.

- 트랜지스터 기반 AND 게이트: 두 개의 트랜지스터가 직렬로 연결되어 입력 신호가 모두 HIGH일 때만 출력이 HIGH로 설정됩니다.

입력 중 하나라도 LOW이면 트랜지스터 중 하나가 전류를 차단하여 출력이 LOW가 됩니다.

논리적 표현: AND 게이트는 논리적 ‘곱셈’과 같은 역할을 하며, 이를 통해 두 개 이상의 조건이 모두 충족되었을 때만 특정 동작을 수행하도록 하는 회로를 만들 수 있습니다.

이 논리적 표현을 이해하는 것이 복잡한 디지털 회로 설계의 기초가 됩니다.

AND 게이트 회로는 많은 전자 시스템에서 사용되며, 특히 조건이 모두 충족되었을 때만 특정 작업을 수행해야 하는 경우에 유용합니다.

예를 들어, 컴퓨터 시스템에서 여러 개의 신호가 동시에 활성화되어야 데이터 전송이 시작되는 것과 같은 시나리오에서 사용될 수 있습니다.

- 연관 참조 : 디지털 논리 게이트, 입.출력, 논리 상태와 전압 레벨

- 연관 참조 : OR 게이트 논리 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : NOT 게이트 논리 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : NAND 게이트 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : NOR 게이트 회로, 회로 구성, 특성 및 성능, 장점 3개와 한계

- 연관 참조 : XOR 게이트 회로 설계, 회로 구성, 특성 및 성능, 장점 3개와 한계

- 연관 참조 : XNOR 게이트 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : Buffer 회로 설계, 회로 설계의 기본 구성, 설계 고려 사항

2. AND 게이트의 회로 구성

AND 게이트는 디지털 논리 회로에서 매우 기본적인 구성 요소로, 다양한 전자 부품을 사용하여 구현할 수 있습니다.

트랜지스터, 다이오드, TTL 및 CMOS 기술을 활용한 AND 게이트 회로의 구성에 대해 살펴보겠습니다.

이러한 구성들은 각각의 특성과 용도에 따라 선택됩니다.

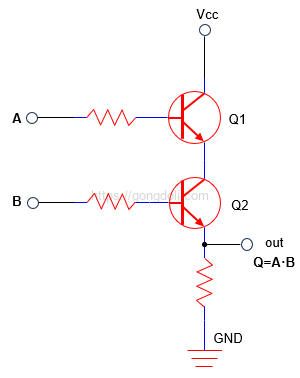

2-1) 트랜지스터를 사용한 AND 게이트

트랜지스터를 사용한 AND 게이트는 가장 일반적인 구현 방식 중 하나입니다. 트랜지스터는 작은 전압이나 전류로 큰 전류를 제어할 수 있는 반도체 소자로, 디지털 회로에서 스위치 역할을 합니다. 트랜지스터 기반의 AND 게이트 회로는 입력이 모두 활성화(1, HIGH)될 때에만 출력이 활성화되도록 설계됩니다.

트랜지스터 기반 2입력 AND 게이트의 동작 원리

트랜지스터를 사용하여 AND 게이트를 구성할 때, 일반적으로 NPN형 트랜지스터 두 개가 사용됩니다.

이 트랜지스터들은 직렬로 연결되어 있으며, 각각의 입력은 베이스(기판)에 연결됩니다.

입력 A와 B가 모두 HIGH일 때만 두 트랜지스터가 동시에 ON 상태가 되어 전류가 흐르게 되고, 결과적으로 출력이 HIGH가 됩니다.

반면, 입력 중 하나라도 LOW이면 해당 트랜지스터가 OFF 상태가 되어 전류가 차단되고 출력은 LOW가 됩니다.

여기서, Q1과 Q2는 NPN 트랜지스터를 나타냅니다.

A와 B는 입력이고, 출력은 두 트랜지스터가 동시에 ON일 때만 활성화됩니다.

- 장점: 트랜지스터 기반 AND 게이트는 상대적으로 저렴하고, 디지털 신호를 안정적으로 처리할 수 있습니다.

- 단점: 이 방식은 트랜지스터 수에 비례하여 복잡성이 증가할 수 있습니다.

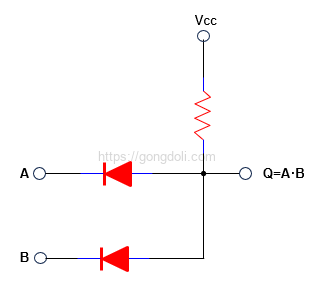

2-2) 다이오드를 사용한 AND 게이트

다이오드를 사용한 AND 게이트는 기본적인 AND 연산을 수행하는 데 매우 간단한 방법입니다.

다이오드는 전류가 한 방향으로만 흐르도록 하는 반도체 소자입니다.

다이오드 기반 AND 게이트는 다이오드와 저항을 이용하여 입력이 모두 HIGH일 때만 출력이 HIGH가 되도록 설계됩니다.

다이오드 기반 2입력 AND 게이트의 동작 원리

두 개의 다이오드가 병렬로 연결되어 있으며, 각 다이오드의 캐소드(음극)는 공통으로 연결되어 출력으로 이어집니다.

입력 신호는 다이오드의 애노드(양극)에 연결됩니다.

입력 A와 B가 모두 HIGH일 때, 두 다이오드가 모두 역바이어스 되어 전류가 흐르지 않고, 따라서 출력이 HIGH가 됩니다.

입력 중 하나라도 LOW이면 해당 다이오드가 순바이어스 되어 전류가 흐르게 되며, 출력이 LOW가 됩니다.

아래는 다이오드 기반 AND 게이트 회로의 예입니다

D1과 D2는 다이오드입니다.

A와 B가 모두 HIGH일 때만 출력이 HIGH가 됩니다.

- 장점: 다이오드 기반 AND 게이트는 매우 간단하고 비용이 저렴합니다.

- 단점: 출력 전압이 정확히 0V 또는 Vcc가 되지 않으며, 여러 개의 다이오드를 사용하면 신호 손실이 발생할 수 있습니다.

2-3) TTL 및 CMOS 기술을 사용한 AND 게이트

TTL (Transistor-Transistor Logic) 및 CMOS (Complementary Metal-Oxide-Semiconductor) 기술은 현대 디지털 회로에서 널리 사용되는 두 가지 주요 논리 회로 기술입니다.

이 두 기술은 각각 고유한 특성과 이점을 가지고 있으며, 다양한 응용 분야에서 사용됩니다

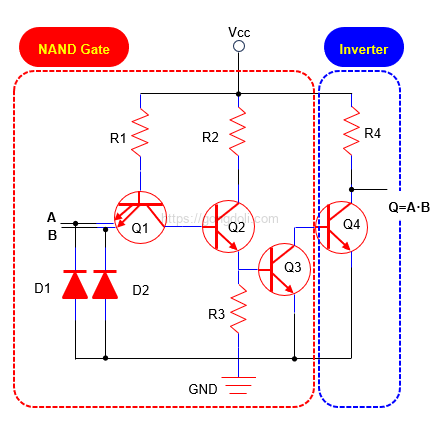

2-3-1) TTL 기반 AND 게이트

TTL 회로는 트랜지스터를 사용하여 논리 연산을 수행합니다.

일반적으로 NPN 트랜지스터와 저항을 포함하며, TTL 7400 시리즈 IC에서 AND 게이트를 포함하는 회로를 찾을 수 있습니다.

TTL 회로는 빠른 스위칭 속도와 중간 정도의 전력 소모를 특징으로 합니다.

전압 수준은 0V(LOW)와 5V(HIGH)로 정의됩니다.

- TTL AND 게이트 회로의 동작 원리

입력이 모두 HIGH일 때 출력이 HIGH가 됩니다.

입력 중 하나라도 LOW일 경우, 출력은 LOW가 됩니다.

아래는 TTL 기반 2입력 AND 게이트의 기본 회로입니다

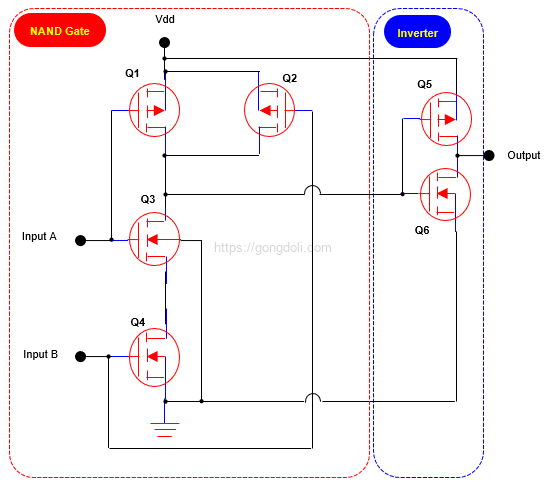

2-3-2) CMOS 기반 AND 게이트

CMOS 회로는 N채널 및 P채널 MOSFET(금속산화물 반도체 전계 효과 트랜지스터)를 사용하여 논리 연산을 수행합니다.

CMOS 4000 시리즈 IC에서 AND 게이트를 찾을 수 있습니다.

CMOS 회로는 매우 낮은 전력 소모와 고속 스위칭을 제공합니다.

전압 수준은 일반적으로 0V(LOW)와 3V-18V(HIGH)로 정의됩니다.

- CMOS AND 게이트 회로의 동작 원리

두 MOSFET가 모두 ON일 때만 전류가 흐르지 않아 출력이 HIGH가 됩니다.

하나라도 OFF일 경우 출력은 LOW가 됩니다.

아래는 CMOS 기반 2입력 AND 게이트의 기본 회로입니다.

2-3-3) TTL과 CMOS의 비교

- 전력 소모: CMOS는 TTL에 비해 전력 소모가 매우 낮습니다.

- 속도: TTL은 CMOS에 비해 빠른 스위칭 속도를 제공합니다.

- 전압 레벨: CMOS는 더 넓은 전압 범위를 지원하며, TTL은 고정된 5V 전압을 주로 사용합니다.

3. AND 게이트의 특성 및 성능

디지털 논리 회로에서 AND 게이트는 매우 중요한 역할을 합니다.

AND 게이트 회로는 입력 신호가 모두 ‘1’일 때만 출력이 ‘1’이 되는 논리 연산을 수행합니다.

3-1) 입력 및 출력 특성

AND 게이트 회로는 두 개 이상의 입력과 하나의 출력을 갖는 디지털 논리 게이트입니다.

기본적인 2입력 AND 게이트를 예로 들어 설명해 보겠습니다.

- 입력 특성

전압 레벨: AND 게이트 회로의 입력 전압은 디지털 상태로 정의됩니다.

일반적으로 TTL 기반 회로에서는 ‘0’은 0V에서 0.8V 사이, ‘1’은 2V에서 5V 사이로 정의됩니다.

CMOS 기반 회로에서는 ‘0’은 0V에서 1.5V 사이, ‘1’은 3V에서 18V 사이입니다.

전류 요구: 입력 신호가 논리적 ‘1’을 제공할 때 회로는 일정한 전류를 필요로 합니다.

이 전류 요구량은 TTL과 CMOS 기술에 따라 다릅니다.

TTL의 경우, 입력 전류는 작지만 CMOS는 거의 전류를 소비하지 않습니다.

- 출력 특성

- 출력 전압 레벨: 출력은 입력에 따라 ‘0’ 또는 ‘1’로 설정됩니다.

TTL 기반의 AND 게이트 회로에서는 출력이 논리적 ‘1’일 때는 Vcc에 가깝고, ‘0’일 때는 0V에 가깝습니다.

CMOS는 보다 넓은 전압 범위를 지원하며, 논리적 ‘1’일 때는 거의 Vdd, 논리적 ‘0’일 때는 거의 0V입니다.

출력 전류: 출력단이 다른 논리 게이트를 구동할 수 있는 전류 용량도 중요합니다.

TTL은 높은 출력 드라이브 능력을 제공하며, CMOS는 낮은 전력 소모로 인해 드라이브 능력이 제한적일 수 있습니다.

3-2) 게이트의 응답 시간

AND 게이트 회로의 응답 시간은 입력 신호가 변화한 후 출력 신호가 변화하는 데 걸리는 시간을 의미합니다.

이 특성은 논리 회로의 성능을 결정짓는 중요한 요소입니다.

- 전파 지연 (Propagation Delay)

전파 지연은 입력 신호가 논리적 상태를 변경한 후 출력 신호가 안정된 상태로 전환되는 데 걸리는 시간입니다.

이 시간은 게이트 내부에서 신호가 전달되고 처리되는 속도에 따라 달라집니다.

TTL 기반 AND 게이트는 일반적으로 빠른 전파 지연을 갖지만, 고전력 소모가 수반될 수 있습니다.

CMOS 기반 AND 게이트는 상대적으로 느릴 수 있지만, 최근 기술 발전으로 인해 매우 빠른 응답 시간을 제공할 수 있습니다.

- 상승 시간과 하강 시간 (Rise and Fall Time)

상승 시간은 출력이 논리적 ‘0’에서 ‘1’로 변할 때 걸리는 시간입니다.

하강 시간은 출력이 논리적 ‘1’에서 ‘0’으로 변할 때 걸리는 시간입니다.

이 두 시간은 게이트의 응답 속도를 평가하는 중요한 기준이며, TTL과 CMOS에서 각각 다르게 나타납니다.

응답 시간은 고속 디지털 회로에서 중요한 요소로, 높은 주파수에서 신호 왜곡을 방지하고 정확한 타이밍을 보장하기 위해 고려되어야 합니다.

3-3) 전력 소비 특성

AND 게이트 회로의 전력 소비는 시스템의 전반적인 에너지 효율에 중요한 영향을 미칩니다.

전력 소비는 특히 배터리로 구동되는 휴대용 장치에서 매우 중요합니다.

- 정적 전력 소모 (Static Power Consumption)

회로가 신호를 처리하지 않고 대기 상태에 있을 때 소비되는 전력입니다.

TTL AND 게이트는 대기 상태에서도 비교적 높은 전력을 소비합니다.

이는 BJT 기반의 트랜지스터가 항상 일정한 전류를 필요로 하기 때문입니다.

CMOS AND 게이트는 대기 상태에서 매우 낮은 전력을 소비합니다.

이는 MOSFET이 활성 상태에서만 전류를 소모하기 때문입니다.

- 동적 전력 소모 (Dynamic Power Consumption)

신호가 변화하면서 회로가 전환될 때 소비되는 전력입니다.

회로의 전환 속도와 빈도에 따라 동적 전력 소모가 결정됩니다.

TTL AND 게이트는 빠른 전환 속도로 인해 비교적 높은 동적 전력을 소비합니다.

CMOS AND 게이트는 전환 시에만 전력을 소모하며, 일반적으로 TTL보다 낮은 동적 전력 소모를 자랑합니다.

- 전력 소모 계산

전력 소모는 회로의 작동 주파수와 부하 조건에 따라 달라집니다.

AND 게이트 회로의 전력 소모를 줄이기 위해 설계자는 회로의 빈번한 전환을 최소화하고, 적절한 전력 관리 기술을 활용해야 합니다.

AND 게이트 회로는 다양한 전자 시스템에서 중요한 역할을 합니다.

입력 및 출력 특성, 응답 시간, 전력 소비 특성을 이해하는 것은 이러한 게이트를 효과적으로 설계하고 활용하는 데 필수적입니다.

이와 같은 디지털 논리 게이트의 특성을 고려하여 적절한 기술을 선택하고, 최적의 성능을 달성하는 것이 중요합니다.

4. AND 게이트의 장점과 한계

AND 게이트 회로는 디지털 논리 회로에서 필수적인 구성 요소 중 하나입니다.

여러 전자 시스템과 회로에서 널리 사용되는 이 게이트는 다양한 장점을 제공하지만, 일부 한계도 존재합니다.

4-1) AND 게이트의 주요 장점

AND 게이트 회로는 간단하면서도 매우 강력한 기능을 제공하여 많은 장점을 가지고 있습니다.

4-1-1) 단순한 설계

AND 게이트 회로는 단순한 트랜지스터 또는 다이오드 배열로 구성할 수 있어, 설계가 비교적 쉽고 직관적입니다.

이 때문에 회로의 물리적 구현과 복잡성이 낮아집니다.

예를 들어, 두 개의 NPN 트랜지스터를 사용한 간단한 AND 게이트 회로는 직관적으로 이해하기 쉽고 구현하기도 간단합니다.

4-1-2) 기본 연산의 구현

AND 게이트 회로는 기본적인 논리 연산인 AND 연산을 수행합니다.

이는 여러 디지털 시스템에서 중요한 기능으로, 두 입력이 모두 ‘1’일 때만 출력을 ‘1’로 설정합니다.

이 기본적인 연산은 복잡한 논리 회로를 구성하는 데 필수적이며, 다양한 컴퓨터 연산 및 디지털 처리를 가능하게 합니다.

4-1-3) 디지털 시스템의 필수 요소

AND 게이트 회로는 다양한 디지털 시스템의 기본 빌딩 블록으로 사용됩니다.

프로세서, 메모리, 제어 시스템 등에서 AND 게이트는 논리 연산을 수행하는 핵심 역할을 합니다.

예를 들어, 프로세서의 ALU(Arithmetic Logic Unit)에서는 AND 게이트를 사용하여 조건부 명령을 수행하거나, 특정 조건이 충족되었는지 확인합니다.

4-1-4) 결정적인 논리 기능

AND 게이트 회로는 명확하고 결정적인 출력을 제공하여 디지털 시스템에서 신뢰할 수 있는 동작을 보장합니다.

두 입력 모두가 ‘1’일 때만 출력이 ‘1’이 되므로, 정확한 논리적 판단을 수행할 수 있습니다.

4-2) AND 게이트의 한계와 단점

AND 게이트 회로는 여러 장점에도 불구하고, 특정 상황에서는 한계와 단점이 존재합니다.

4-2-1) 입력 상태의 제한

AND 게이트 회로의 출력이 ‘1’이 되기 위해서는 모든 입력이 ‘1’이어야 합니다.

따라서, 특정 응용에서는 출력이 ‘1’이 될 확률이 매우 낮을 수 있습니다.

예를 들어, 다수의 입력을 갖는 AND 게이트에서 모든 입력이 ‘1’이 될 확률은 매우 낮아질 수 있으며, 이는 출력이 자주 ‘0’이 되는 결과를 초래할 수 있습니다.

4-2-2) 다수 입력 처리의 비효율성

입력이 많아질수록 AND 게이트 회로의 설계가 복잡해질 수 있으며, 다중 입력의 경우 회로의 응답 시간이 길어질 수 있습니다.

이는 고속 회로 설계에서 문제가 될 수 있습니다.

다중 입력을 처리하기 위해 여러 AND 게이트를 직렬로 연결하면, 총 전파 지연 시간이 증가하여 전체 시스템의 속도를 저하시킬 수 있습니다.

4-2-3) 전력 소모

TTL 기반 AND 게이트 회로는 작동 중 비교적 높은 전력을 소비할 수 있으며, 이는 전력 효율이 중요한 응용에서는 단점이 될 수 있습니다.

예를 들어, TTL 게이트는 대기 상태에서도 전력을 소비하므로, 전력 관리가 중요한 시스템에서는 CMOS 기반의 대안을 고려해야 합니다.

4-2-4) 아날로그 간섭에 대한 민감성

AND 게이트 회로는 입력 신호의 아날로그 특성에 민감할 수 있습니다.

노이즈나 불안정한 전압이 입력에 영향을 미치면, 게이트의 출력이 올바르게 나타나지 않을 수 있습니다.

이러한 문제는 디지털 신호가 왜곡되거나 잡음이 많을 경우 AND 게이트 회로의 성능에 영향을 줄 수 있습니다.

4-3) 다른 논리 게이트와의 비교

AND 게이트 회로를 다른 기본 논리 게이트와 비교해 보면, 각각의 게이트는 고유의 특성과 용도를 가지고 있습니다.

- AND 게이트 회로는 특정 조건이 모두 충족되는지 확인할 때 유용합니다.

반면에 OR 게이트는 하나 이상의 조건이 성립되는 경우에 사용됩니다. - NOT 게이트는 단일 입력의 반대 논리를 제공하며, 매우 단순한 설계를 가지고 있습니다.

- NAND 게이트와 NOR 게이트는 기본 게이트로서 널리 사용되며, AND와 OR의 부정형태를 제공하여 복잡한 논리 회로를 구성할 때 유용합니다.

- XOR 게이트와 XNOR 게이트는 비트 비교 및 고급 연산에서 사용되며, 비교적 복잡한 논리 연산을 처리할 수 있습니다.

What i don’t realize is actually how you’re not actually much more well-liked than you might be right now. You’re so intelligent. You realize thus considerably relating to this subject, produced me personally consider it from so many varied angles. Its like women and men aren’t fascinated unless it’s one thing to do with Lady gaga! Your own stuffs nice. Always maintain it up!

Thank you for your incredibly kind words!Your support means a lot, and I’ll continue to do my best to provide valuable insights and information

I couldn’t resist commenting

I’m really glad you did! ,thank you!

I’m really enjoying the design and layout of your blog. It’s a very easy on the eyes which makes it much more enjoyable for me to come here and visit more often. Did you hire out a developer to create your theme? Great work!

Thank you so much for the lovely feedback!

I’m thrilled to hear that the design makes your visits more enjoyable.

The theme was carefully chosen and customized to keep things clean and user-friendly

Great write-up, I’m regular visitor of one’s website, maintain up the nice operate, and It is going to be a regular visitor for a long time.

That’s such a kind message—thank you!

It means a lot to know you’re a regular visitor and that the content keeps you coming back

I?¦ve been exploring for a little bit for any high-quality articles or blog posts in this kind of space . Exploring in Yahoo I eventually stumbled upon this website. Reading this info So i?¦m satisfied to show that I’ve an incredibly excellent uncanny feeling I discovered just what I needed. I most indisputably will make certain to don?¦t put out of your mind this site and give it a glance regularly.

So glad you found it—thanks for coming by!

Hello, I think your blog might be having browser compatibility issues. When I look at your website in Safari, it looks fine but when opening in Internet Explorer, it has some overlapping. I just wanted to give you a quick heads up! Other then that, wonderful blog!

Thanks for the heads-up!

I’ll look into it.

The next time I read a blog, I hope that it doesnt disappoint me as much as this one. I mean, I know it was my choice to read, but I actually thought youd have something interesting to say. All I hear is a bunch of whining about something that you could fix if you werent too busy looking for attention.

Thank you for sharing your honest thoughts.

I’ll keep your feedback in mind to improve.

Have you ever considered about adding a little bit more than just your articles? I mean, what you say is fundamental and everything. But imagine if you added some great photos or video clips to give your posts more, “pop”! Your content is excellent but with images and video clips, this blog could certainly be one of the best in its field. Awesome blog!

Thank you! I appreciate your suggestion and will keep it in mind for future posts.

I like this blog very much, Its a real nice position to read and receive info . “The love of nature is consolation against failure.” by Berthe Morisot.

Thank you! I appreciate your kind words and the beautiful quote.

I went over this site and I believe you have a lot of excellent information, saved to favorites (:.

Thank you for your kind words. I’m glad you found the information valuable enough to save.

I have not checked in here for some time because I thought it was getting boring, but the last several posts are great quality so I guess I will add you back to my everyday bloglist. You deserve it my friend 🙂

Thank you for your kind words. I’m glad the recent posts brought you back to the bloglist.

A large percentage of of what you assert happens to be supprisingly accurate and that makes me wonder the reason why I hadn’t looked at this in this light previously. Your article really did turn the light on for me as far as this particular topic goes. Nevertheless there is actually one particular issue I am not too comfy with so while I attempt to reconcile that with the core idea of your point, permit me observe exactly what all the rest of the readers have to say.Well done.

Thank you so much for your thoughtful feedback! I’m glad the article offered a new perspective, and I truly appreciate your openness in sharing both what resonated and what felt challenging.

Hello There. I found your blog using msn. This is a very well written article.

I will make sure to bookmark it and come back to read more of your useful info.

Thanks for the post. I’ll certainly return.

Thank you so much for your kind words! I’m glad you enjoyed the article. I truly appreciate you bookmarking the blog

Wow that was unusual. I just wrote an extremely long comment but after I clicked submit my comment

didn’t appear. Grrrr… well I’m not writing

all that over again. Anyways, just wanted to say wonderful blog!

Thank you very much! I’m glad you like the blog.