1. Buffer 회로 설계란 무엇인가?

1-1) Buffer 회로의 정의

Buffer 회로는 입력 신호를 변형하지 않고 출력으로 전달하는 회로입니다.

일반적으로 전압이나 전류 증폭기처럼 동작하지만, 입력 신호를 단순히 증폭하는 것이 아니라, 출력과 입력 간의 분리를 통해 부하 효과를 최소화합니다.

Buffer 회로는 다음과 같은 두 가지 주요 특성을 가지고 있습니다.

- 입력 저항이 매우 높음: 입력 신호를 거의 손실 없이 회로로 전달할 수 있도록 합니다.

- 출력 저항이 매우 낮음: 부하에 강력한 신호를 제공할 수 있어 부하의 영향을 받지 않고 신호를 안정적으로 전달합니다.

이러한 특성 때문에 Buffer 회로 설계는 전자 회로에서 신호의 전송, 증폭, 분리 등에 매우 유용하게 사용됩니다.

예를 들어, 어떤 센서가 출력하는 신호가 매우 약할 때, 이 신호를 직접 다른 회로로 전달하면 신호가 크게 왜곡될 수 있습니다.

이때 Buffer 회로를 사용하면 신호가 왜곡되지 않도록 할 수 있습니다.

1-2) Buffer 회로 설계의 필요성

Buffer 회로 설계는 다음과 같은 이유로 필수적입니다.

- 신호 무결성 유지 : 긴 배선이나 다양한 부하에 의해 신호가 왜곡되는 것을 방지합니다.

Buffer 회로는 고임피던스 소스를 저임피던스 부하로 안전하게 연결할 수 있게 해줍니다.

예를 들어, 아날로그 신호가 긴 케이블을 통해 전송될 때, 신호가 약해지거나 왜곡될 수 있습니다.

Buffer 회로는 이러한 신호를 증폭하여 왜곡 없이 다음 단계로 전달합니다. - 신호 증폭 : Buffer 회로는 신호의 크기를 증가시키지 않지만, 신호의 전송을 개선합니다.

이를 통해 약한 신호가 다른 회로로 전달될 때 강하게 전달될 수 있도록 합니다.

예를 들어, 마이크로컨트롤러의 출력이 다른 고전력 회로를 구동하기에는 너무 약한 경우, Buffer 회로가 필요합니다. - 회로 분리 : Buffer 회로는 입력과 출력 사이의 전기적 연결을 차단하여 입력 회로와 출력 회로 간의 상호 간섭을 방지합니다.

이는 특히 서로 다른 전원 레벨을 사용하는 회로 간의 인터페이스에서 중요합니다.

예를 들어, A/D 변환기와 디지털 회로 간의 연결에서 Buffer 회로는 두 회로 간의 간섭을 방지합니다. - 전력 구동 능력 향상 : Buffer 회로는 출력 전력 용량을 증가시켜, 더 많은 부하를 구동할 수 있도록 합니다.

이는 LED 디스플레이나 모터와 같은 고전력 부하를 제어할 때 매우 유용합니다.

- 연관 참조 : 디지털 논리 게이트, 입.출력, 논리 상태와 전압 레벨

- 연관 참조 : AND 게이트 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : OR 게이트 논리 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : NOT 게이트 논리 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : NAND 게이트 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : NOR 게이트 회로, 회로 구성, 특성 및 성능, 장점 3개와 한계

- 연관 참조 : XOR 게이트 회로 설계, 회로 구성, 특성 및 성능, 장점 3개와 한계

- 연관 참조 : XNOR 게이트 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

2. Buffer 회로 설계의 기본 구성 요소

Buffer 회로 설계는 악기 신호, 특히 기타와 같은 전자 악기의 신호를 안정적으로 유지하는 데 필수적인 구성 요소입니다.

특히, 신호를 왜곡시킬 수 있는 다른 회로에서, 고주파 성분의 손실을 방지하는 역할을 합니다.

Buffer 회로 설계는 간단하고 비용 효율적으로 구현할 수 있으며, Buffer 회로는 또한 이펙트 회로의 출력 단에도 적용할 수 있어, 전체적인 신호 품질을 유지하는 데 도움을 줍니다.

2-1) 기본 Buffer 회로

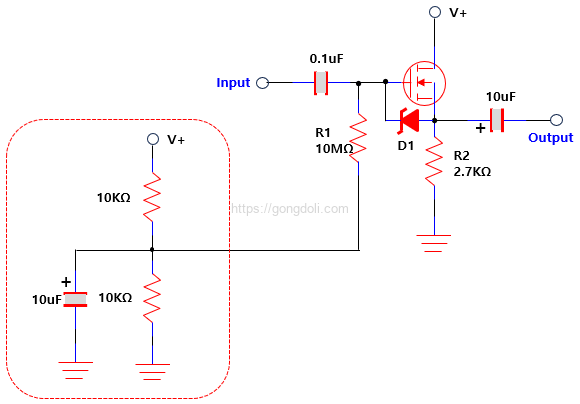

Buffer 회로 설계의 가장 기본적인 형태는 JFET(접합형 전계효과 트랜지스터)를 사용한 공통 드레인(Common Drain) 증폭기입니다.

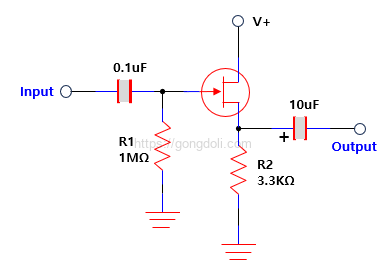

2-1-1) JFET 공통 드레인 증폭기

이 회로에서 입력 임피던스는 저항 R1의 값에 의해 결정되며, 일반적으로 1MΩ으로 설정됩니다.

이는 기타와 같은 고임피던스 신호 소스에 적합합니다.

R2는 게이트 바이어스를 안정화시키기 위한 저항으로, 3.3kΩ에서 10kΩ 사이의 값을 사용할 수 있습니다.

이 회로의 간단한 구성 덕분에 최소한의 부품만으로 구현할 수 있지만, 입력 전압이 게이트-소스 전압과 소스의 바이어스 전압을 초과할 경우 신호가 클리핑될 수 있습니다.

이 회로는 간단하면서도 효과적인 버퍼링을 제공하여 신호의 로딩을 방지하고 기타의 원래 음색을 유지하는 데 유리합니다.

이 JFET Buffer 회로의 출력 임피던스는 JFET 자체의 특성에 따라 결정되며, 일반적으로 수백 Ω 수준입니다.

2-1-2) 응용 예시

기본 JFET Buffer 회로는 기타의 신호가 이펙트 페달을 통과할 때 발생할 수 있는 음질 손실을 방지하기 위해, 빈티지 와와 페달 앞에 자주 사용됩니다. 이는 고주파 응답을 유지하고, 기타의 원래 사운드를 왜곡 없이 전달하는 데 도움을 줍니다.

2-2) 개선된 JFET Buffer 회로

JFET Buffer 회로 설계는 그 자체로도 훌륭한 성능을 발휘하지만, 특정 상황에서는 성능을 더욱 향상시킬 수 있는 방법들이 있습니다.

그 중 하나는 게이트 바이어스를 설정하는 방식입니다.

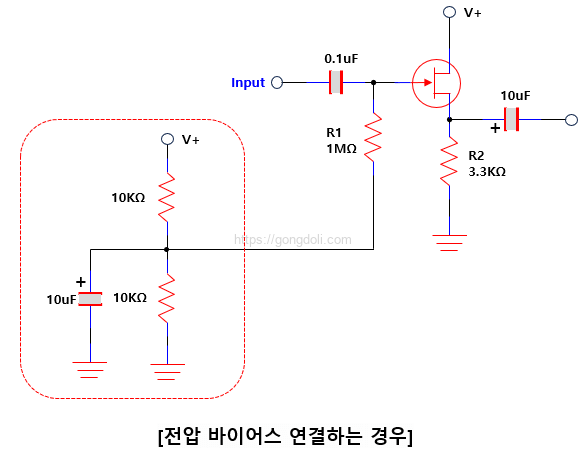

일반적으로, JFET Buffer 회로에서 게이트 저항은 접지에 연결되어 있으나, 이를 바이어스 전압에 연결하면 더 나은 결과를 얻을 수 있습니다.

게이트 저항을 바이어스 전압에 연결하는 방법

- JFET의 게이트 저항을 접지 대신 바이어스 전압에 연결하면, 소스의 바이어스 전압이 더 높은 값으로 설정되어 헤드룸이 증가합니다.

이 방식은 입력 신호가 클리핑 없이 더 큰 범위까지 처리될 수 있도록 도와줍니다. - 입력 임피던스는 여전히 R1의 값에 의해 결정됩니다.

- 고출력의 험버커 픽업이나 피에조 센서와 같은 고임피던스 신호 소스를 사용할 경우, R1의 값을 10MΩ 이상으로 증가시켜 입력 임피던스를 높게 유지할 수 있습니다.

- R1의 값이 증가하면, 더 깨끗한 소리가 제공되지만, 값이 높아질수록 회로에서 약간의 열 잡음이 추가될 수 있습니다.

이 개선된 JFET Buffer 회로는 특히 고임피던스 소스에서 더 큰 신호를 처리해야 할 때 유용합니다.

회로의 입력 임피던스가 증가하면서 신호의 왜곡 없이 더 넓은 다이내믹 레인지를 처리할 수 있게 됩니다.

2-3) 전압 분배를 이용한 JFET Buffer 회로

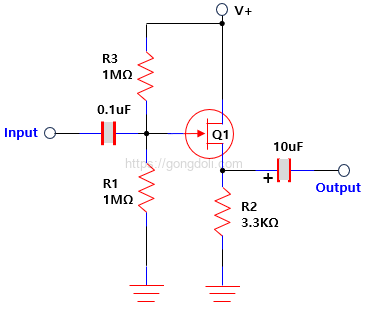

바이어스 전압 소스가 없거나, 추가적인 부품을 최소화하고 싶은 경우에는 전압 분배를 이용하여 게이트 바이어스를 설정할 수 있습니다.

이 방식은 회로의 부품 수를 줄이고, 바이어스 전압 소스가 필요 없는 상황에서도 효과적으로 JFET Buffer 회로를 구성할 수 있게 해줍니다.

전압 분배를 이용한 JFET Buffer 회로

- 이 회로에서는 게이트 바이어스를 두 개의 저항(R2, R3)으로 설정합니다.

- 이 저항들은 전압 분배기 역할을 하여 적절한 바이어스 전압을 제공합니다.

- 이 방법을 통해 바이어스 전압 소스가 없는 경우에도 게이트 바이어스를 설정할 수 있습니다.

- 입력 임피던스는 R1과 R3의 병렬 값으로 계산됩니다.

예를 들어, R1과 R3가 각각 1MΩ이라면, 입력 임피던스는 500kΩ이 됩니다. - 이를 2MΩ 이상으로 쉽게 증가시켜 1MΩ의 입력 임피던스를 유지할 수 있습니다.

- 이 회로는 Envelope Filter와 같은 고감도 신호 처리 장치의 입력 부분에서 자주 사용됩니다.

이 전압 분배를 이용한 JFET Buffer 회로는 구성 요소가 적으며, 비교적 간단한 설정으로 고성능을 유지할 수 있습니다.

특히, 특정한 바이어스 전압 소스를 필요로 하지 않는 상황에서 유용하게 사용할 수 있습니다.

이와 같이, Buffer 회로 설계는 다양한 상황에 맞춰 최적화할 수 있으며, 입력 신호의 특성에 따라 적절한 방법을 선택하는 것이 중요합니다.

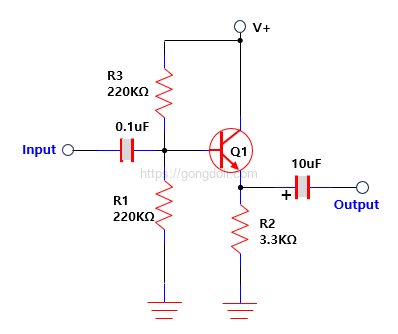

2-4) 바이폴라 트랜지스터를 사용한 Buffer 회로

Buffer 회로 설계에서 가장 일반적으로 사용되는 부품 중 하나는 바이폴라 트랜지스터입니다.

JFET만큼 높은 입력 임피던스는 제공하지 않지만, 바이폴라 트랜지스터는 몇 가지 중요한 장점이 있습니다.

바이폴라 트랜지스터를 사용한 Buffer 회로는 일반적으로 더 낮은 출력 임피던스를 제공하며, 부품을 쉽게 구할 수 있어 다양한 응용 분야에 적합합니다.

바이폴라 트랜지스터를 사용한 Buffer 회로의 주요 특징

- 입력 임피던스: 바이폴라 트랜지스터를 사용한 Buffer 회로의 입력 임피던스는 JFET 회로보다 낮지만, 대부분의 응용에서는 충분히 높습니다.

이 회로는 일반적으로 수십에서 수백 킬로옴의 입력 임피던스를 가집니다. - 출력 임피던스: 바이폴라 트랜지스터 회로는 매우 낮은 출력 임피던스를 제공하며, 이는 수십에서 수백 옴 사이에 있습니다.

이러한 낮은 출력 임피던스는 다음 단계로 신호를 효과적으로 전달하는 데 유리합니다. - 구성 요소의 가용성: 바이폴라 트랜지스터는 전자 부품 시장에서 쉽게 구할 수 있어, 다양한 회로 설계에 유리합니다.

바이폴라 트랜지스터를 사용한 기본적인 Buffer 회로는 간단하지만, 매우 효과적입니다.

예를 들어, 기타 신호를 처리하는 애플리케이션에서는 이 회로가 신호의 저하 없이 안정적인 출력을 제공할 수 있습니다.

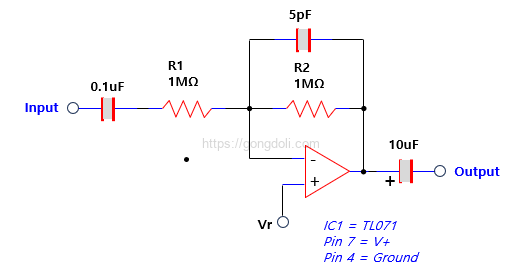

2-5) MOSFET을 사용한 Buffer 회로

Buffer 회로 설계에서 MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)을 사용하는 또 다른 접근 방식이 있습니다.

MOSFET은 바이폴라 트랜지스터와 유사한 기능을 제공하지만, 몇 가지 독특한 특성 덕분에 특정 응용 분야에서 더 적합할 수 있습니다.

MOSFET을 사용한 Buffer 회로의 주요 특징

- 정전기 보호: MOSFET의 게이트는 매우 민감하여 정전기 방전(ESD)으로 쉽게 손상될 수 있습니다.

이를 방지하기 위해 MOSFET 게이트에 9V 제너 다이오드(D1)를 추가하여 보호 회로를 구성할 수 있습니다. - 입출력 임피던스: MOSFET은 높은 입력 임피던스와 낮은 출력 임피던스를 제공하여 신호 전달을 효과적으로 관리할 수 있습니다.

이는 고주파 신호를 처리할 때 특히 유용합니다. - 고주파 감쇠: MOSFET은 전극 간 높은 커패시턴스를 가지고 있어, 고주파 감쇠가 발생할 수 있습니다.

따라서, 고주파 신호를 유지해야 하는 애플리케이션에서는 회로 설계에 주의를 기울여야 합니다.

MOSFET Buffer 회로 설계는 AMZ Mosfet Booster의 버퍼 모드와 유사합니다.

여기서 중요한 점은 MOSFET의 고유한 특성을 최대한 활용하여 신호의 왜곡을 최소화하고, 안정적인 출력을 제공하는 것입니다.

이 회로는 기타나 오디오 애플리케이션뿐만 아니라, 다양한 전자 기기에서도 널리 사용됩니다.

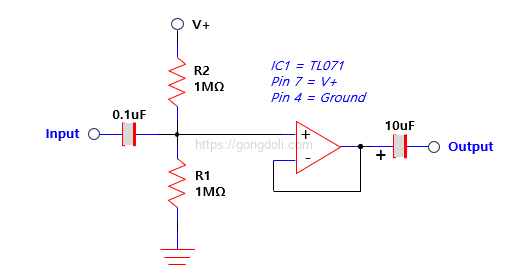

2-6) OPAMP를 사용한 Buffer 회로

Buffer 회로 설계에서 OPAMP(연산 증폭기)는 트랜지스터 기반의 회로보다 우수한 성능을 제공합니다.

OPAMP를 사용한 Buffer 회로는 신호를 왜곡 없이 유니티 게인(unity gain)으로 증폭하며, 매우 낮은 출력 임피던스를 갖는다는 점에서 특히 유리합니다.

이는 수십 옴 단위의 낮은 출력 임피던스를 제공하여, 신호의 전송을 안정적이고 효율적으로 만듭니다.

2-6-1) OPAMP를 사용한 Buffer 회로의 주요 특징

- 정확한 unity gain: OPAMP Buffer 회로는 신호의 크기를 변경하지 않고 그대로 출력합니다.

이는 신호 증폭에 있어 중요한 안정성과 신뢰성을 제공합니다. - 매우 낮은 출력 임피던스: OPAMP 회로는 트랜지스터 기반의 회로보다 훨씬 낮은 출력 임피던스를 제공하며, 이는 수십 옴 단위로 측정됩니다.

낮은 출력 임피던스는 신호의 손실을 최소화하고 다음 단계로의 신호 전달을 용이하게 합니다. - 간단한 구성: OPAMP를 사용한 Buffer 회로는 구성 요소의 수가 적으며, 단순한 설계로 복잡하지 않은 회로를 구성할 수 있습니다.

OPAMP를 사용한 Buffer 회로 설계의 또 다른 중요한 점은, 전압 분배를 이용한 바이어싱이 가능하다는 것입니다.

이는 트랜지스터 기반의 Buffer 회로와 유사한 방식으로 입력 임피던스를 계산할 수 있습니다.

2-6-2) OPAMP Buffer 회로의 동작 원리

이 OPAMP Buffer 회로는 입력 신호를 반전시키는 특징이 있습니다.

이 특성은 후속 증폭 단계에서 신호를 다시 반전시킴으로써 출력 신호가 입력 신호에 비해 비반전 상태가 되도록 합니다.

이는 동일한 소스에서 나온 다른 신호와 혼합할 때 신호가 상쇄되지 않도록 하는 데 중요합니다.

- 입력 임피던스: 이 회로의 입력 임피던스는 R1 값에 의해 결정됩니다.

R1 값은 회로가 처리할 수 있는 신호 소스의 특성에 따라 조정될 수 있습니다. - 출력 신호의 정밀도: OPAMP의 특성 덕분에, 이 회로는 입력 신호를 매우 정확하게 출력으로 전달합니다.

따라서 OPAMP Buffer 회로는 신호의 품질을 유지하면서 증폭이 필요한 응용에 이상적입니다.

예를 들어, 오디오 애플리케이션에서 OPAMP Buffer 회로는 기타 또는 다른 악기 신호의 품질을 유지하면서 여러 이펙트 회로를 통과할 수 있도록 도와줍니다.

OPAMP 회로는 다양한 전자기기 및 신호 처리 시스템에서도 광범위하게 사용됩니다.

이러한 특성 덕분에, OPAMP를 사용한 Buffer 회로는 고품질의 신호 처리와 안정적인 출력이 요구되는 많은 전자 애플리케이션에서 필수적인 역할을 합니다.

이 회로는 또한 구성 요소의 간단함과 높은 신뢰성 덕분에 설계와 구현이 용이합니다.

3. Buffer 회로 설계 시 고려 사항

Buffer 회로 설계는 신호의 왜곡 없이 원래의 성질을 유지하면서 신호를 전송하는 중요한 역할을 합니다.

이를 위해서는 여러 가지 기술적 요소를 고려해야 합니다.

3-1) 입력 및 출력 특성

Buffer 회로 설계에서 입력 및 출력 특성은 매우 중요합니다.

이러한 특성은 회로가 다양한 신호 조건에서 어떻게 작동하는지를 결정합니다.

- 입력 임피던스 : Buffer 회로는 일반적으로 높은 입력 임피던스를 가져야 합니다.

높은 입력 임피던스는 신호 소스(예: 기타 픽업, 센서 등)가 최소한의 전력으로 Buffer에 신호를 전달할 수 있게 합니다.

예를 들어, 트랜지스터 기반 Buffer 회로는 1MΩ 이상의 입력 임피던스를 가질 수 있습니다.

이렇게 하면 소스 신호에 거의 부하를 주지 않으므로 신호 왜곡이 최소화됩니다. - 출력 임피던스 : 반대로, Buffer 회로는 낮은 출력 임피던스를 가져야 합니다.

낮은 출력 임피던스는 Buffer 회로가 후속 회로로 신호를 강력하게 전달할 수 있도록 해줍니다.

이로 인해 신호의 전송 손실이 줄어들고, 출력 신호의 품질이 유지됩니다.

일반적으로 OPAMP 기반 Buffer 회로는 수십 Ω의 매우 낮은 출력 임피던스를 가지고 있어 효과적인 신호 전달이 가능합니다.

Buffer 회로 설계는 신호의 왜곡 없이 원래의 성질을 유지하면서 신호를 전송하는 중요한 역할을 합니다. 이를 위해서는 여러 가지 기술적 요소를 고려해야 합니다. 아래에서는 Buffer 회로 설계 시 주요 고려 사항인 입력 및 출력 특성, 신호 무결성과 응답 시간, 전력 소비와 효율성에 대해 자세히 설명하겠습니다.

3.1 입력 및 출력 특성

Buffer 회로 설계에서 입력 및 출력 특성은 매우 중요합니다. 이러한 특성은 회로가 다양한 신호 조건에서 어떻게 작동하는지를 결정합니다.

- 입력 임피던스: Buffer 회로는 일반적으로 높은 입력 임피던스를 가져야 합니다. 높은 입력 임피던스는 신호 소스(예: 기타 픽업, 센서 등)가 최소한의 전력으로 Buffer에 신호를 전달할 수 있게 합니다. 예를 들어, 트랜지스터 기반 Buffer 회로는 1MΩ 이상의 입력 임피던스를 가질 수 있습니다. 이렇게 하면 소스 신호에 거의 부하를 주지 않으므로 신호 왜곡이 최소화됩니다.

- 출력 임피던스: 반대로, Buffer 회로는 낮은 출력 임피던스를 가져야 합니다. 낮은 출력 임피던스는 Buffer 회로가 후속 회로로 신호를 강력하게 전달할 수 있도록 해줍니다. 이로 인해 신호의 전송 손실이 줄어들고, 출력 신호의 품질이 유지됩니다. 일반적으로 OPAMP 기반 Buffer 회로는 수십 오옴의 매우 낮은 출력 임피던스를 가지고 있어 효과적인 신호 전달이 가능합니다.

3-2) 신호 무결성과 응답 시간

Buffer 회로는 신호의 무결성을 유지하면서 빠르게 응답해야 합니다.

이를 위해서는 다음과 같은 요소를 고려해야 합니다.

- 신호 무결성 : 신호 무결성은 Buffer 회로가 입력 신호를 왜곡 없이 출력으로 전달하는 능력을 의미합니다.

이를 위해, Buffer 회로 설계는 신호의 주파수 응답, 왜곡, 그리고 노이즈 수준을 고려해야 합니다.

OPAMP를 사용하는 Buffer 회로는 일반적으로 매우 낮은 왜곡과 넓은 주파수 응답을 제공합니다.

이러한 특성은 고주파수 응답이 중요한 오디오 애플리케이션에 매우 유리합니다. - 응답 시간 : 응답 시간은 Buffer 회로가 입력 신호의 변화를 얼마나 빨리 따라갈 수 있는지를 나타냅니다.

이는 특히 빠른 신호 전환이 중요한 디지털 회로에서 중요합니다.

Buffer 회로의 응답 시간을 최적화하려면 회로의 대역폭과 스위칭 속도를 고려해야 합니다.

예를 들어, OPAMP 기반 Buffer 회로는 고속 신호 처리에 적합한 높은 대역폭을 가질 수 있습니다.

3-3) 전력 소비와 효율성

Buffer 회로의 전력 소비와 효율성도 중요한 고려 사항입니다.

이는 특히 배터리로 구동되는 장치나 저전력 애플리케이션에서 중요합니다.

- 전력 소비 : Buffer 회로는 신호를 증폭하지 않기 때문에 일반적으로 낮은 전력을 소비합니다.

그러나, 사용되는 트랜지스터나 OPAMP의 종류에 따라 소비 전력이 달라질 수 있습니다.

예를 들어, CMOS 기술을 사용하는 Buffer 회로는 매우 낮은 전력 소비를 특징으로 합니다.

이는 저전력 애플리케이션에서 매우 유용합니다. - 효율성 : 회로의 효율성은 신호 처리 동안 소모되는 전력과 출력되는 신호의 품질 사이의 균형을 유지하는 능력을 의미합니다.

Buffer 회로 설계에서는 고효율을 유지하면서도 입력 신호의 왜곡 없이 출력을 제공할 수 있어야 합니다.

이를 위해서는 회로 설계 시 전력 관리와 열 관리가 중요합니다.

이렇게 Buffer 회로 설계에서는 입력 및 출력 특성, 신호 무결성과 응답 시간, 전력 소비와 효율성 등 다양한 요소를 고려해야 합니다.

이러한 요소들을 최적화함으로써, 고품질의 신호 전달과 효율적인 전력 사용을 보장할 수 있습니다.

I’ve been absent for some time, but now I remember why I used to love this blog. Thank you, I will try and check back more often. How frequently you update your site?

Thank you for your kind words! I’m thrilled to have you back.I will try to update it regularly.

whoah this blog is magnificent i love reading your articles. Keep up the good work! You know, many people are hunting around for this info, you could help them greatly.

Thank you so much for your wonderful feedback! It’s incredibly rewarding to hear that the articles resonate with you and provide valuable insights.

Hiya, I am really glad I have found this info. Nowadays bloggers publish just about gossips and net and this is actually frustrating. A good site with interesting content, that’s what I need. Thanks for keeping this website, I will be visiting it. Do you do newsletters? Can not find it.

Thanks so much for your kind words—they truly mean a lot!

I’m really glad you found the site refreshing and helpful.

As for newsletters, I don’t currently offer one, but it’s a great idea and I’ll definitely keep it in mind for the future. In the meantime, feel free to drop by anytime!

Just want to say your article is as astounding. The clarity in your post is simply nice and i can assume you are an expert on this subject. Fine with your permission let me to grab your feed to keep updated with forthcoming post. Thanks a million and please keep up the enjoyable work.

Thank you so much for your incredibly kind words!

I’m truly honored that you found the article clear and insightful.

There are some attention-grabbing closing dates in this article however I don’t know if I see all of them heart to heart. There’s some validity but I will take hold opinion until I look into it further. Good article , thanks and we would like more! Added to FeedBurner as properly

Thank you for your thoughtful comment and for subscribing via FeedBurner!

I appreciate your honest take.

Virtually all of the things you assert happens to be astonishingly precise and that makes me ponder the reason why I had not looked at this with this light previously. This piece truly did turn the light on for me as far as this specific subject matter goes. Nonetheless there is 1 factor I am not too comfortable with and whilst I make an effort to reconcile that with the actual core theme of your position, let me see just what the rest of the visitors have to point out.Nicely done.

Thank you so much for such a thoughtful and reflective comment.

I’m truly glad this piece helped shed new light on the topic for you.

Thankyou for this tremendous post, I am glad I noticed this website on yahoo.

I truly appreciate your kind words!

It’s great to know that Yahoo led you here and that the post made a strong impression.

so much fantastic information on here, : D.

Glad you’re enjoying it—thanks for stopping by!

I adore foregathering useful information , this post has got me even more info! .

Thank you for your kind words. I’m glad this post provided you with more helpful information.

Wow! This could be one particular of the most useful blogs We’ve ever arrive across on this subject. Actually Great. I am also an expert in this topic so I can understand your effort.

Thank you very much for your generous compliment. I truly appreciate your recognition of the effort.