Contents

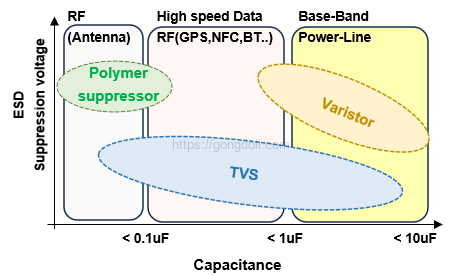

1. 대표적인 ESD 보호 부품 종류

회로를 설계할 때 ESD(정전기 방전) 보호를 고려하는 것이 중요합니다.

특히, ESD 보호 부품 선택과 배치 과정에서 TVS 다이오드와 바리스터 중 어떤 것을 사용할지 고민하는 경우가 많습니다.

TVS 다이오드(TVS Diode, Transient Voltage Suppression Diode)는 ESD와 같은 순간적인 고전압 스파이크를 빠르게 억제하기 위해 만들어진 속도가 매우 빠른 보호 소자입니다.

평상시에는 거의 전류가 흐르지 않지만, 정해진 전압 이상이 순간적으로 들어오면 바로 도통되어 과전압을 바이패스시킵니다.

일반적인 정류 다이오드와는 다르게, 수 ns(나노초) 이내 반응속도를 가지기 때문에 민감한 IC 보호에 적합합니다.

예를 들어, CMOS 회로나 USB 회로에 외부에서 정전기(수 kV 이상)가 순간적으로 유입될 경우, TVS 다이오드는 이 전압을 흡수하고 접지로 흘려보내 회로를 보호합니다.

바리스터(Varistor)는 전압에 따라 저항값이 바뀌는 부품입니다.

평상시에는 고저항이지만, 일정 전압 이상이 되면 급격히 저항이 낮아져 전류를 흘려보냅니다.

TVS보다 반응 속도가 조금 느리며, 고에너지 서지(낙뢰 유입 서지, 전원선 서지 등)에 강합니다.

일반적으로 AC 라인, 파워 회로, 대용량 보호 회로에 많이 사용됩니다.

예를 들어, 220V 전원에 낙뢰로 2,000V 이상 순간 전압이 유입될 때, 바리스터가 전류를 우회시켜 회로를 보호합니다.

참고로, TVS는 작은 충격에 빠르게 반응하고, 바리스터는 큰 충격에 견디는 역할입니다.

보완적으로 함께 사용하는 경우도 많습니다.

왜 둘 다 알아야 하는가?

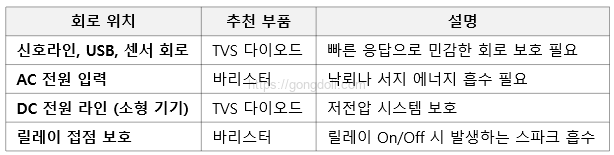

ESD 보호 부품 선택과 배치 가이드에서는 이 두 부품을 어떻게 조합해서 쓸지 결정하는 것이 매우 중요합니다.

예를 들어, 정밀 센서가 있는 아날로그 회로에는 TVS 다이오드를 쓰고, 전원 입력 쪽에는 바리스터를 배치하는 것이 일반적입니다.

이런 구성은 보호 성능 + 회로 노이즈 관리 두 마리 토끼를 잡는 방법이 됩니다.

TVS 다이오드와 바리스터는 모두 정전기로부터 회로를 보호하는 훌륭한 부품입니다. 하지만 성격이 조금 다르기 때문에 회로의 위치, 쓰임새에 따라 적절한 선택이 필요합니다. ESD 보호 부품 선택과 배치를 이해하고, 제품의 특성을 잘 파악한다면 불량률을 줄이고 제품의 신뢰성을 높이는 중요한 포인트가 됩니다.

- 연관 참조 : ESD 유형별 차이점,HBM,CDM,MM,HIM 비교, 특징 3가지

- 연관 참조 : ESD EOS Surge 차이, EOS, Surge, 차이점 비교

- 연관 참조 : 정전기 방지 대책,필요 이유,점검 순서,대책 기본 원칙

- 연관 참조 : 정전기 접지 관리 방법, 작업별 접지 작업 수칙 및 방법

- 연관 참조 : 정전기 측정 방법, 주요 정전기 측정 장비 및 측정 방법

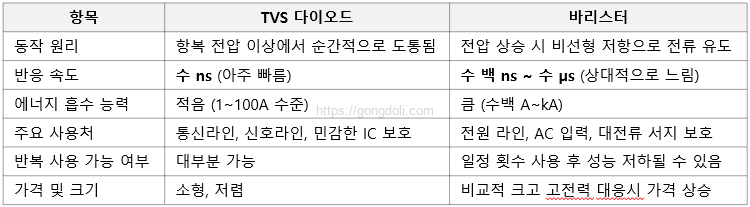

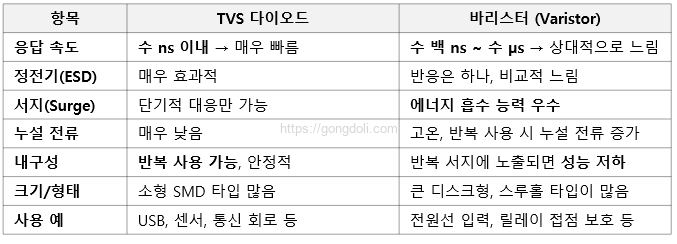

2. TVS vs 바리스터

회로 설계를 할 때 가장 중요한 고민 중 하나는 ESD 보호 부품 선택과 배치입니다.

ESD 보호 부품으로 TVS 다이오드를 써야 할까?, 아니면 바리스터를 써야 할까?

두 부품 모두 회로를 외부의 정전기나 과도 전압으로부터 보호해 주는 역할을 하지만, 작동 조건과 성능 특성이 다르기 때문에 용도에 맞게 선택해야 합니다.

왜 ESD 보호 부품 선택과 배치가 중요할까요?

ESD 보호 부품 선택과 배치는 제품의 내구성과 신뢰성에 직접적인 영향을 줍니다.

예를 들어, 민감한 마이크로컨트롤러 앞에 바리스터를 넣는 실수를 하면, 느린 응답 속도 때문에 정전기를 제때 막지 못하고 IC가 손상될 수 있습니다.

반대로 전원선에 TVS 다이오드만 달아놨다면, 낙뢰에 의한 고에너지 서지 전압을 버티지 못할 수 있습니다.

따라서 회로의 위치, 부하 특성, 위험 요소를 종합적으로 고려한 ESD 보호 부품 선택과 배치가 필수입니다.

간단하게 정리하면 빠르고 민감한 보호는 TVS, 크고 거친 서지에 강한 보호는 바리스터입니다.

정전기(ESD)와 서지(Surge)는 다릅니다.

(자세한 내용은 ESD EOS Surge 차이, EOS, Surge, 차이점 비교)

초보자 분들이 가장 많이 혼동하는 부분입니다.

둘 다 ‘과전압’이지만, 성격과 발생 위치, 에너지 크기가 전혀 다릅니다.

예를 들어, 사람이 손으로 만졌을 때 발생하는 ESD는 짧고 날카로운 전압으로, 민감한 IC를 파괴할 수 있기 때문에 TVS 다이오드가 빠르게 대응해줘야 합니다.

반면, 전원 라인에 낙뢰 유도 전압이 들어오는 경우엔 바리스터처럼 큰 에너지를 흡수할 수 있는 부품이 필요합니다.

언제 TVS를 쓰고, 언제 바리스터를 쓸까?

실제 설계할때는 TVS와 바리스터를 조합해서 쓰는 경우도 많습니다.

예를 들면, 바리스터로 큰 서지를 막고, TVS로 잔여 전압을 빠르게 클램핑하는 식으로 사용합니다.

ESD 보호 부품 선택과 배치는 단순히 제품 데이터시트만 보고 결정하는 게 아닙니다.

보호하려는 대상이 무엇인지, 어떤 종류의 위협(ESD or 서지)이 존재하는지, 그리고 반복 보호가 필요한지까지 고려해야 합니다.

정전기나 서지 문제는 “설계할 때 미리 대응하면 0원, 나중에 대응하면 몇 천만 원”이라는 말이 있을 정도로, 설계 초기부터 신경 써야 할 부분입니다.

ESD 보호 부품 선택과 배치는 기기의 안정성과 제품 수율을 좌우하는 중요한 요소입니다.

TVS와 바리스터, 어떤 게 더 좋다고 단정 지을 수는 없습니다.

대신 각각의 특성과 회로 상황을 고려해 올바른 위치에 배치하는 것, 그게 진짜 중요한 포인트입니다.

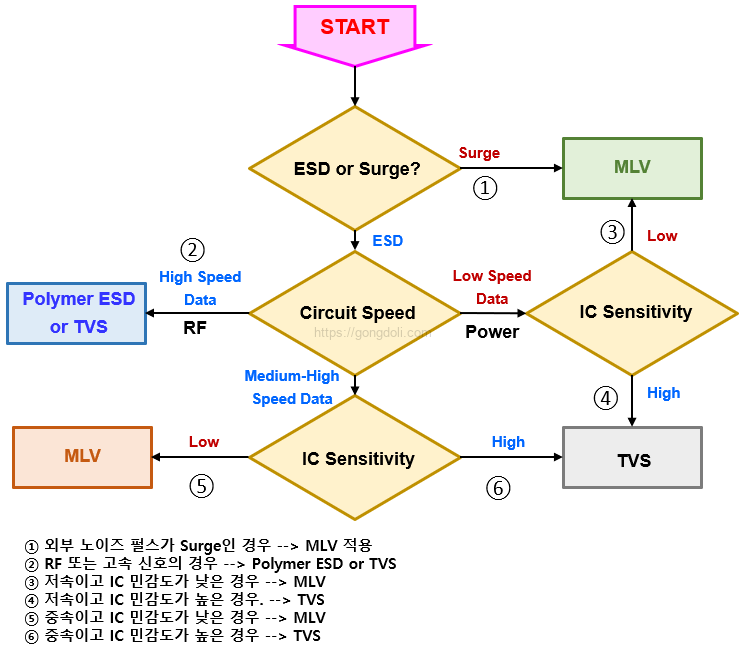

3. ESD 대책 부품 선택 방법

ESD(정전기 방전)는 IC를 고장내는 대표적인 원인 중 하나입니다.

이를 예방하려면 회로 특성에 따라 적절한 ESD 보호 부품 선택과 배치가 꼭 필요합니다.

하지만 실무에서는 어떤 회로에는 TVS 다이오드를 사용하고, 어떤 회로에는 MLV(멀티레이어 바리스터), 또 어떤 회로에는 Polymer ESD 부품을 사용해야 하니, ESD 보호 부품 선택과 배치 기준이 헷갈리는 경우가 많습니다.

ESD 대책 부품 선택과 배치는 단순히 싸고 작은 부품을 고르는 일이 아닙니다.

보호 대상 IC의 민감도, 회로의 신호 속도, 동작 전압 등 다양한 요소를 종합적으로 고려해야 합니다.

ESD인지 Surge인지, 고속인지 저속인지, 민감한 회로인지 아닌지를 먼저 구분하고, 그에 맞는 TVS, MLV, Polymer ESD 등을 알맞게 선택하는 것. 그게 바로 성공적인 회로 설계의 기본이자 ESD 대책 부품 선택과 배치의 핵심입니다.

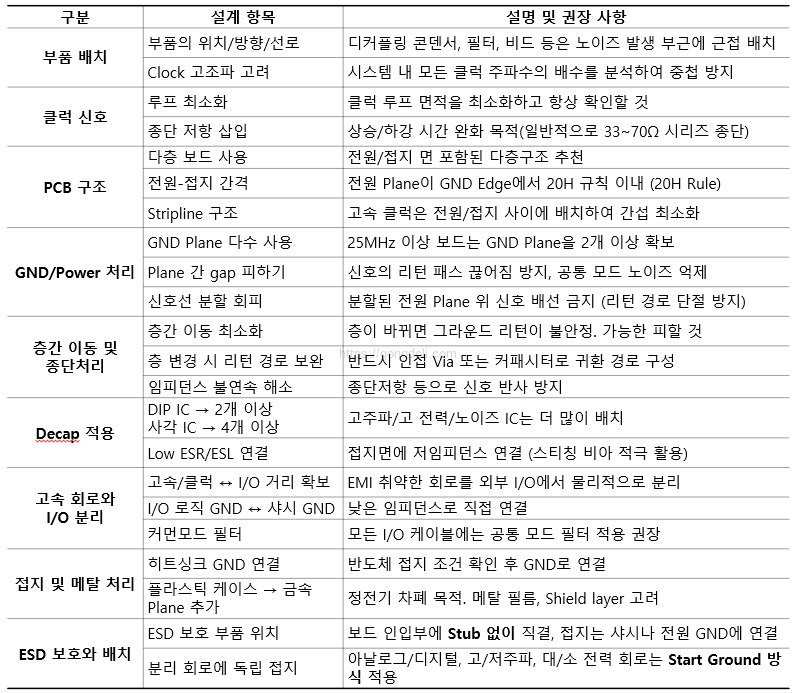

4. ESD 보호 부품의 올바른 PCB 배치

ESD 보호 부품 선택과 배치는 설계 후반이 아닌 초기에 전략적으로 계획되어야 합니다.

특히 고속 클럭 신호와 외부 인터페이스가 동시에 있는 회로에서는 EMC, ESD 대책이 겹치므로 보호 회로, 접지, 레이아웃을 동시에 고려해야 합니다.

ESD 보호 부품은 단독으로 쓰는 것보다 올바른 GND 배치 및 필터링 회로와의 조합이 효과적입니다.

5. 저잡음 PCB 설계를 위한 주의사항

PCB 설계하면서 “왜 이렇게 잡음이 많지?”, “IC가 오동작하네?” 하는 경우, 전원/접지 쪽에 문제가 있을 가능성이 큽니다.

이럴 땐 디커플링 커패시터 위치, 접지 설계, 루프 면적 같은 기본적인 것부터 다시 점검해봐야 합니다.

특히 요즘처럼 고속 신호가 많은 회로에서는, ESD 보호 부품 선택과 배치도 잡음과 오동작의 원인이 되기 때문에 함께 고려해야 합니다.

아무리 회로가 잘 짜여 있어도, ESD 보호 부품을 적절히 선택하지 않거나 PCB에 제대로 배치하지 않으면, 외부 정전기나 스파이크 전압이 내부 회로에 침투해 노이즈를 유발하고, 결국 IC가 오작동하게 됩니다.

따라서 디커플링 커패시터 배치뿐 아니라, ESD 보호 부품 선택과 배치까지 포함해서 종합적으로 설계를 검토하는 것이 중요합니다.

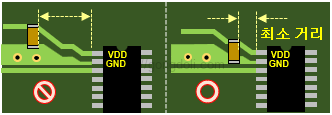

5-1) 디커플링 커패시터는 IC 전원 핀에 최대한 가깝게 배치하자

많은 분들이 디커플링 커패시터를 전원 트레이스 선상에만 달면 된다고 생각합니다.

사실 가장 중요한 건 IC 전원 핀(VDD) 근처, 그것도 바로 옆에 붙여주는 겁니다.

커패시터에서 IC까지의 선이 짧고 굵어야 효과가 살아납니다.

왜냐면, Decoupling 커패시터는 말 그대로 전류를 ‘디커플’ 해서, IC가 순간적으로 전류를 많이 먹을 때, 그걸 보조해주는 역할을 합니다.

전원에서 오는 긴 선로를 통해 공급받으려면 타이밍이 늦고, 그 사이 잡음이 생깁니다.

그래서 IC 바로 옆에서 딱 받쳐줘야 합니다.

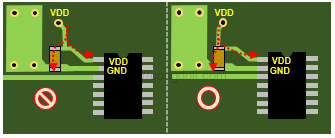

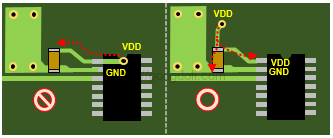

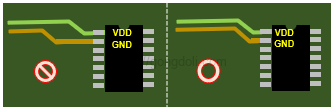

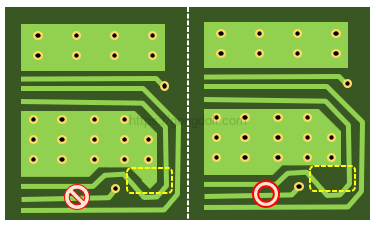

5-2) 전원 배선은 “전원 → 커패시터 → IC” 순서로

이건 간과하기 쉬운 부분입니다.

IC로 가는 전원 라인 중간에 Decoupling 커패시터를 넣어야지, 옆으로 삐져나오게(stub 형태) 배치하면 효과가 줄어듭니다.

이유는 간단합니다.

Stub 구조는 선로 인덕턴스를 늘리고, 그만큼 커패시터가 IC에 영향을 주기 어려워지기 때문입니다.

또한, 아래처럼 전원⇒IC(VDD핀)⇒Decap으로 배선되면 IC핀(VDD)과 Decap간의 선로 인덕턴스에 의해 Decoupling 효과가 반감됩니다.

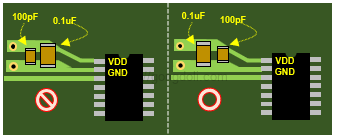

5-3) 용량이 작은 커패시터를 더 가까이, 큰 것은 바깥쪽

디커플링 커패시터를 여러 개 달 때는 순서가 중요합니다.

고속 잡음 제거용으로 디커플링 커패시터 용량이 작은(예: 0.1µF, 100pF)것을 사용하는 경우에는 IC 바로 옆에 배치하고

저주파 안정화용으로 커패시터 용량 큰것(예: 1µF, 10µF)을 사용하는 경우에는 약간 바깥쪽에 배치합니다.

왜 이렇게 하냐면, 작은 커패시터일수록 내부 인덕턴스(ESL)가 작고 반응 속도가 빠르기 때문입니다.

그러니까 순간적인 노이즈를 먼저 제거하고, 큰 용량은 천천히 충전되면서 전압을 안정시켜주는 겁니다.

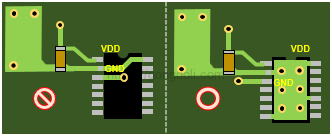

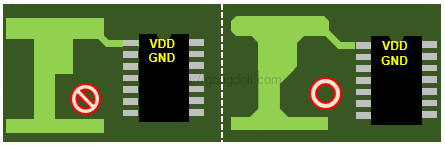

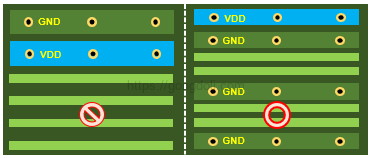

5-4) IC 밑에는 GND 면을 충분히 깔고, Via를 여러 개 뚫어라

IC 밑에 GND Plane을 두는 건 EMI 억제를 위한 가장 기본적인 팁입니다.

여기에 여러 개의 Via로 GND를 연결해주면 저임피던스 경로가 확보되어, 잡음이 훨씬 덜 생깁니다.

이렇게 하면 두 가지 효과가 있습니다.

- IC 자체의 노이즈가 외부로 퍼지는 걸 막아줍니다. (EMI 차폐 효과)

- 안정적인 GND 레벨을 유지할 수 있어 디커플링 성능이 올라갑니다.

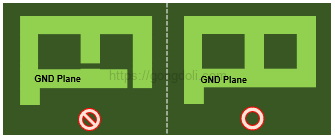

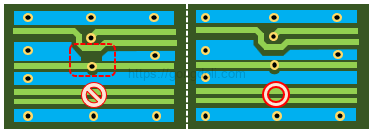

5-5) GND 패턴은 가능한 한 닫힌 루프(폐루프) 형태로 설계하자

이건 초보자들이 많이 실수하는 부분입니다.

GND를 그냥 둘러만 놓고 입구와 출구가 끊겨 있는 오픈 루프 구조로 만들면, 신호가 돌다가 갈 길을 잃습니다.

그러면 불필요한 루프 전류나 공진이 생겨서 오히려 잡음이 더 생깁니다.

⇒ 가급적 폐루프 형태로 넓게, 그리고 루프 면적은 작게 설계하는 게 좋습니다.

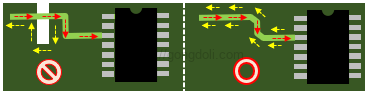

5-6) 전원과 접지 배선은 꼭 붙여서 따라가야 한다 (루프 면적 최소화)

전류는 전원선을 타고 흐르고 GND를 통해 돌아옵니다.

이 두 선로가 멀리 떨어져 있으면, 그 사이의 루프 면적이 커져서 마치 안테나처럼 EMI를 방출하게 됩니다.

이런 EMI는 ESD 충격 시 발생하는 고속 트랜지언트 신호와 공진되기 쉽고, 주변 IC에 영향을 주는 경로가 됩니다.

따라서 전원과 접지 배선은 꼭 붙여서, 루프 면적을 최소화해야 합니다.

이건 단순히 EMI 문제뿐 아니라, ESD 보호 부품 선택과 배치 후에도 효과를 제대로 내기 위한 필수 조건입니다.

ESD 전류도 결국은 귀환경로를 타고 흐르기 때문입니다.

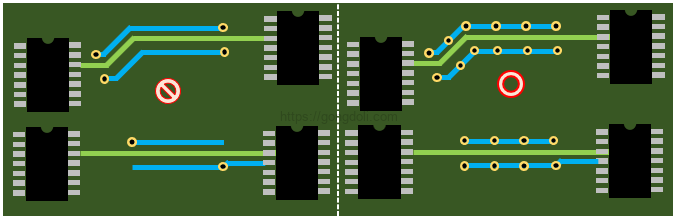

5-7) 전원/신호 배선은 90도 꺾지 말자 (45도 또는 곡선으로!)

배선을 90도로 꺾으면, 그 모서리에서 고주파 신호가 반사되거나 집중적으로 방사되는 경향이 있습니다.

특히 고속 회로나 정전기 방전 시, ESD 서지에 의해 이런 꺾인 지점이 노이즈 방출의 핫스팟이 되기 쉽습니다.

그래서 전원선이나 고속 신호선은 항상 부드럽게 꺾고, 가능하면 45도나 곡선 형태로 처리해야 합니다.

이렇게 해야 ESD 보호 부품을 아무리 잘 선택하고 배치해도 그 효과가 감소하지 않습니다.

ESD 보호는 단순히 부품만으로 끝나는 게 아니라, 전체적인 배선 구조와 함께 고려돼야 합니다.

5-8) 고속 신호 배선은 90도 금지! GND Plane 위에서 귀환경로 확보하기

고속 신호는 속도가 빠르기 때문에 그 리턴 전류도 바로 아래 GND Plane을 기준으로 흐릅니다.

이때 Plane에 Split이나 Gap이 있으면, 리턴 전류가 우회하거나 튀게 되어 EMI가 심각해질 수 있습니다.

그리고 이런 지점은 ESD 충격 시 서지 전류가 잘못 분산되는 경로가 되기 때문에, ESD 보호 소자의 배치 효과도 떨어집니다.

고속 신호 배선은 항상 연속적인 GND Plane 위에서 배선하고, 꺾임 없이 부드럽게 처리해야 합니다.

이렇게 해야 ESD 보호 부품 선택과 배치가 효과적으로 작동합니다.

아무리 좋은 TVS 다이오드를 써도, 리턴 경로가 엉망이면 보호가 제대로 되지 않기 때문입니다.

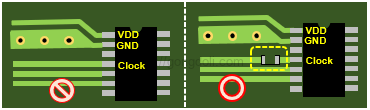

5-9) 발진소자(Crystal, OSC)는 짧고 조용한 곳에 배치

발진소자는 IC에 클럭을 공급하는 핵심 부품이지만, 동시에 잡음의 근원이 될 수도 있습니다.

발진선로에서 발생하는 고조파는 고속 노이즈로 작용하고, 외부 방사뿐 아니라 ESD 유입 시 다시 재발진 또는 오동작의 트리거가 되기도 합니다.

해결 방법은 다음과 같습니다.

- IC와 발진소자를 최대한 가깝게 배치하고

- 선로는 짧고 굵게

- 주위는 GND로 감싸서 방사 억제

- 아래나 옆에 전원/고속 신호선이 지나가지 않도록 배치

이런 설계 구조는 ESD 보호 부품을 발진소자 주변에 배치할 때도 효과적입니다.

ESD는 의외로 클럭 회로를 타고 IC 내부에 침투하기 쉬운데, 이를 막기 위해서는 부품의 선택뿐 아니라 배선 구조까지 세심하게 고려해야 합니다.

5-10) 고속 신호선은 GND와 짝지어 설계하고, 리턴 경로를 확보하자

고속 신호선은 항상 GND와 짝지어 움직여야 합니다.

이건 신호 품질 유지뿐 아니라 ESD 충격 시 전류 경로 확보에도 핵심적인 설계 포인트입니다.

- 신호선 바로 아래 연속된 GND Plane 확보

- GND와 짝(Pair) 형태로 배선 (가능하면 Differential Pair)

- 다른 고속 신호와는 3W Rule로 Crosstalk 최소화

- GND Guard 추가로 방사 억제

이렇게 하면, TVS 다이오드나 페라이트 비드 같은 ESD 보호 부품 선택과 배치했을 때 그 효과를 극대화할 수 있습니다.

아무리 좋은 부품이라도, 리턴 경로나 접지면이 설계가 잘못되어 있으면 정전기 충격을 제대로 흘려보낼 수 없습니다.

5-11) 고속 신호 출력 단자에는 예비용 패드(Land)를 준비하자

고속 신호, 특히 Clock 신호는 반사나 고조파로 인해 EMI, Crosstalk, ESD 오동작을 유발할 수 있습니다.

이때 댐핑 저항(수십 Ω)을 직렬로 삽입하면 반사 문제를 크게 줄일 수 있지만, 설계 초기에 반드시 필요한지 판단하기 어려울 수 있습니다.

그래서 출력 라인에는 ESD 보호 부품 선택과 배치를 고려하여 댐핑 저항이나 페라이트 비드용 예비 패드를 반드시 준비해두는 것이 좋습니다.

이 예비 패드는 필요할 경우 댐핑 저항을 넣고, 필요 없다면 0Ω 저항이나 솔더 브리지로 연결하면 됩니다.

또한, 해당 저항은 IC의 출력 핀 근처에 배치해야, ESD 충격이 유입될 때 가장 앞단에서 흡수 및 제어가 가능합니다

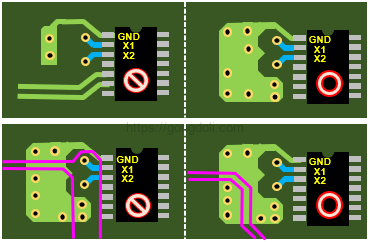

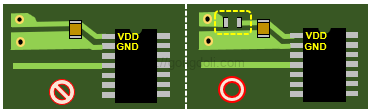

5-12) IC 전원 핀에는 반드시 Decoupling Capacitor를 인접하게 배치

IC 전원 핀 근처에 디커플링 캐패시터(Decap)를 붙이는 것은 노이즈 억제의 기본입니다.

하지만 보통 설계 초기에 공간이나 배선상 이유로 캐패시터를 묶어서 한곳에 두는 경우가 있습니다.

이러면 IC별로 전원 노이즈 억제 효과가 불균일해지고, 특히 ESD 충격 시 전류가 예상 외의 경로로 흐르며 문제를 유발할 수 있습니다.

ESD 보호 부품 선택과 배치의 효과를 극대화하기 위해서는, 각 IC 전원 핀 근처에 각각 Decap을 붙이는 것이 필수입니다.

또한 전원과 Decap 사이에 페라이트 비드(Bead)를 넣을 수 있도록 예비용 패드도 함께 준비해두시면 좋습니다.

문제가 발생했을 때 빠르게 대응할 수 있고, 필요 없을 경우는 역시 0Ω으로 단락하면 됩니다.

5-13) 필터 부품과 신호 선로는 깔끔하게 정렬, 간섭을 피하자

RC 필터, Bead-C 필터 등 노이즈 억제 부품을 배치할 때, 선로가 부품 몸체와 너무 가까우면 필터 효과가 약화됩니다.

선로의 전자기장이 부품에 직접 영향을 주어, 필터 자체가 노이즈의 경로가 될 수도 있습니다.

ESD 보호 부품 선택과 배치 시에도, 해당 부품이 실질적으로 노이즈를 걸러낼 수 있는 구조가 되어야 하며, 이런 배치 정렬을 통해 노이즈가 부품으로 우회하거나 바로 인가되지 않도록 주의해야 합니다.

5-14) 디커플링 캐패시터는 각 IC마다 “별도”로 배치하라

설계가 복잡해질수록 디커플링 캐패시터를 하나의 군으로 묶고 싶어지지만, 이는 각 IC가 필요로 하는 고주파 전류를 안정적으로 공급하지 못하게 만듭니다.

각 IC의 전원 핀 바로 옆에 적어도 1개 이상의 Decap을 배치하고, 비드나 ESD 보호 소자를 연결할 수 있는 예비 패드도 확보해 두시면 좋습니.

이러한 구성은 ESD 충격이 전원라인을 통해 IC에 유입되는 것을 효과적으로 억제하는 구조를 만들어 줍니다.

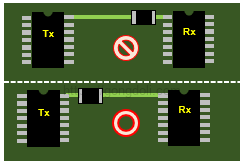

5-15) 직렬 종단 저항은 송신(TX)단 출력 핀 바로 근처에!

신호 라인의 특성 임피던스와 송신단의 출력 임피던스가 맞지 않으면, 반사로 인해 링잉(Ringing)이 발생하고, 이 신호가 ESD 충격 시 공진 경로를 형성할 수도 있습니다.

종단 저항은 수신단이 아니라 송신단(TX)의 출력 핀 근처에 배치해야, 신호 반사 및 ESD 간섭을 최소화할 수 있습니다.

이 위치는 ESD 보호 부품 선택과 배치와도 겹치는 핵심 위치로, 보호 소자와 함께 검토해야 할 주요 포인트입니다.

5-16) 연산 증폭기(OPAMP)의 입력은 Noise에 매우 민감하므로, 저항을 인접 배치하라

OPAMP 입력은 고임피던스이고, 회로 자체가 증폭 기능을 가지기 때문에 아주 작은 노이즈에도 민감하게 반응합니다.

입력 선로가 길어지면 기생 성분이 증가하여 외부 노이즈뿐 아니라 ESD 충격에도 쉽게 영향을 받게 됩니다.

OPAMP 주변의 저항, 캐패시터 등은 반드시 입력 핀 가까이에 배치하시기 바랍니다.

또한, 입력 라인에 ESD 보호 소자를 추가하거나, 보호 소자 삽입을 고려한 예비 패드를 확보해 두는 것이 좋습니다.

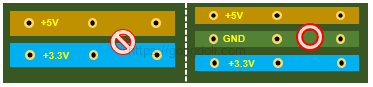

5-17) 서로 다른 전원 선로 간에는 GND Guard를 추가하라

예를 들어 5V와 3.3V 전원선이 동시에 존재하는 시스템에서, 두 선로가 가까이 나란히 배치되면, 전원 간 간섭이 발생하고, 경우에 따라 ESD 충격이 한 전원에서 다른 전원 라인으로 이동할 수 있습니다.

이를 방지하기 위해서는 전원 라인 사이에 GND Guard 라인을 배치하거나 Power Plane 상에서도 GND 영역을 삽입하여 전자기적 차폐를 수행해야 합니다.

이것은 ESD 보호 부품 선택과 배치의 효과를 높이는 구조적 지원 요소이기도 합니다.

5-18) 접지(GND) 선로는 끊어지게 하지 마라.

접지선로는 끊겨있으면 Return path의 불연속을 유발하며 또한 끊어진 접지나 Island 패턴은 방사 Noise의 안테나로 작용할 수 있음으로 접지(GND) 선로는 끊어지게 하지 않아야 합니다.

또한 ESD 전류의 분산 경로가 단절되면 ESD 보호 회로의 효과도 저하될 수 있으므로, ESD 보호 부품 선택과 배치가 효과적으로 작동하려면 GND의 연속성이 필수적입니다.

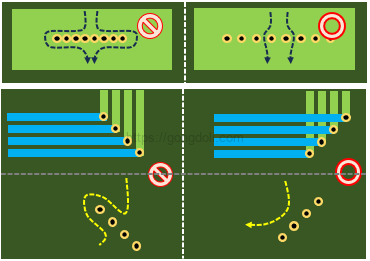

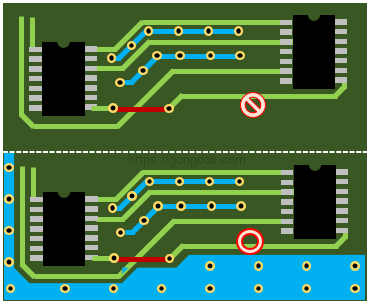

5-19) 귀환 경로(Return path)의 불연속이 없도록 Via를 배치하라.

고속 신호의 리턴패스는 인접한 GND층을 따라 흐르므로, Via 배치가 적절치 않으면 Return path가 우회하게 되어 노이즈가 발생할 수 있습니다.

특히 외부에서 유입되는 정전기 전류(ESD)는 최소 임피던스 경로로 빠르게 접지되어야 하므로, ESD 보호 부품 선택과 배치 후 이들이 효과적으로 GND로 연결되도록 Via를 충분히 확보해야 합니다.

선로의 설계에서 Via의 배치 방향에 따라 Return path가 우회하게 된다. 즉 좌로 45’로 처리한 경우보다 우로 45’로 처리하면 Return path 특성이 개선된다.

5-20) 접지면 Copper fill(Pour)에 의한 잔여 부분(GND Beta)은 제거하라.

접지면 Copper fill(Pour) 작업 후 남는 작은 영역(GND Beta)은 충분한 접지 연결이 없어 안테나 역할을 하며 불필요한 방사 노이즈를 유발합니다.

특히 ESD 보호 부품 선택과 배치 시에도, 접지면의 일관성과 안정성이 확보되어야 부품이 정상 동작할 수 있습니다.

잔여 GND Beta는 제거하거나 충분한 Via로 메인 GND에 연결해야 합니다.

5-21) 기판 외곽은 접지(GND)로 Copper fill(Pour) 하라.

PCB의 외곽은 외부 Noise로부터 영향을 받기 쉬우며 또한 외부로 Noise를 방사하기도 쉽습니다.

따라서 PCB의 외곽은 GND Beta 처리를 해야 합니다.

그리고 일정 간격으로 접지 Via를 처리하여 접지 임피던스를 최소화해야 합니다.

이 구조는 외부로부터 유입되는 정전기(ElectroStatic Discharge)의 차폐에도 도움이 되며, ESD 보호 부품 선택과 배치가 효과를 보이도록 돕는 역할도 합니다.

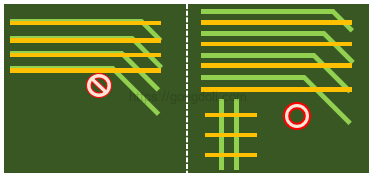

5-22) Clock 라인은 접지(GND) Guard를 배선하고 적정 간격으로 Via 처리한다.

고속선로(Clock)를 따라 접지 Guard를 둘 경우, Guard 선로 상에 한쪽만 Via처리하면 오히려 안테나가 될 수 있습니다.

따라서 적정 간격으로 Via를 처리하여 접지 임피던스를 최소화해야 합니다.

또한 Clock 신호처럼 ESD에 민감한 선로 주변에는 ESD 보호 부품 선택과 배치를 고려하여 보호 회로가 동작할 수 있도록 Guard 및 Via 구조와 연계하여 설계하는 것이 바람직합니다.

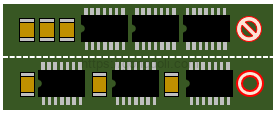

5-23) 인접 층에 신호라인간 겹쳐지는 영역을 피하라.

인접(아래/위층)층 간의 선로 설계 시 겹쳐지는 영역이 많을수록 Crosstalk에 영향을 받기 쉽습니다.

따라서 아래 위 선로가 서로 어긋나게 처리하여야 하며 가장 효과적인 방법은 위 층 선로가 수평이면 바로 아래층은 수직으로 처리하면 Crosstalk를 대부분 줄일 수 있습니다.

그리고 동일 층에서의 선로와 선로 간에도 3W rule(선로 간 간격을 선로 폭의 2배)을 적용해야 합니다.

귀환 경로상에서의 Crosstalk 영향을 줄이기 위해 선로와 Reference층 간의 높이(h)의 2배 이상으로 선로 간 간격을 이격해야 합니다.

5-24) 부품이나 커넥터 패드의 Reference 부위는 제거하여 임피던스를 제어하라.

SATA, USB 3.0 등 1GHz 이상의 고속 신호 선로 설계에서 부품 혹은 커넥터용 패드(Pad)는 Copper 면적이 선로 폭 대비 커짐으로 등가 C값이 증가합니다.

따라서 특성 임피던스 관계식에서 L은 큰 변화가 없는데 C가 증가하여 PAD 영역에서 임피던스가 낮아집니다.

이러한 임피던스 불연속에 의한 반사(Reflection)를 방지하기 위해서 Pad 인접 Reference층에서 Pad 크기에 해당하는 영역을 제거(Cut out)하면 임피던스 변동을 줄일 수 있습니다.

이러한 처리는 차동선로 설계에서 자주 활용된다. Reference층 Pad 영역 제거 시 다른 신호라인의 귀환 경로를 끊지 않도록 유의하여 설계해야 하며, ESD 보호 부품 선택과 배치 후에도 리턴 경로가 안정적으로 확보되도록 고려해야 합니다.

5-25) ADC/DAC의 아날로그와 디지털 전원은 Bead로 Noise를 분리하라.

고속 신호 처리용 ADC/DAC의 전원 공급에 있어 동일 전원으로 아날로그와 디지털 전원을 공급할 경우 전력 소모가 많고 전류 변동이 많은 디지털 부에 먼저 전원을 공급 선로를 연결하고 이 전원을 바로 아날로그 부에 연결하면 디지털 전원 Noise가 유입됨으로 반드시 Bead를 통해 아날로그 부로 전원을 공급해야 합니다.

이때 각 전원 핀에 인접하여 Decap을 배치해야 하며, 고속 신호를 포함하는 ADC/DAC의 경우 ESD 보호 부품 선택과 배치를 통해 정전기 유입으로부터 아날로그 회로를 보호할 수 있습니다.

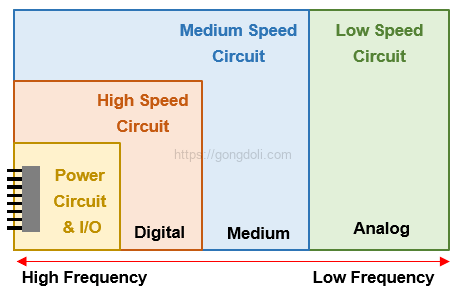

5-26) 회로 Block 배치 시 전원 & I/O → 고속의 Digital부 → 중간(Medium) 속도 → 낮은(Low) 속도 순으로 회로 Block을 배치하라.

처리 신호의 속도가 빠를수록 전원과 외부 인터페이스와 가깝게 배치하고 속도가 느린 쪽은 바깥쪽으로 하는 원칙이 있습니다.

즉 전원(I/O)→ 고주파 → 중간주파 → 저주파 영역의 형태로 나누어야 합니다.

고속 (디지털) 회로는 전력 소모가 많고 전원과 신호 선로의 임피던스가 낮아야 하므로 전원과 I/O 측에 인접시켜야 합니다.

특히 고속 디지털 회로 주변의 외부 인터페이스(I/O) 근처에는 ESD 보호 부품 선택과 배치가 매우 중요하며, TVS 다이오드, ESD Suppressor 등을 포함한 적절한 보호 회로의 사전 고려가 필요합니다.

또한 신호 층에서 전원(VCC)와 접지 선로를 구성할 때 전원/접지 연결은 1점에서 분기하는 형태로의 Layout이 필요합니다.

이를 Star topology PCB layout이라고 하며 각 기능별 Block에서 전원 단과 접지 선로를 통한 상호 간 Noise의 간섭을 최소화할 수 있습니다.

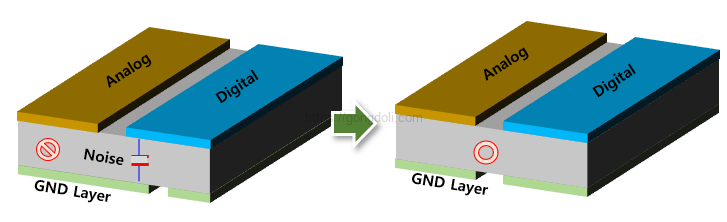

5-27) 기능 블록이 다른 GND면은 신호(전원)층과 서로 겹치지 않도록 분리하라.

아날로그와 디지털, 고주파와 저주파 등 회로의 특성(기능)이 다른 신호/전원 층과 인접한 접지 층은 서로 겹치지 않도록 해야 합니다.

디지털 영역의 신호 영역과 아날로그 접지층이 겹치면 디지털 영역의 Noise가 Capacitive Coupling에 의해 아날로그 접지층으로 유입되어 아날로그 영역에 접지 전압에 영향을 줄 수 있습니다.

단 이렇게 회로 영역별로 분기된 접지면 간에는 1-Point Grounding을 하여 공통 임피던스의 영향을 줄이거나 Bead를 적용하여 고주파 Noise의 간섭을 배제할 수 있습니다.

Nice blog here! Also your website loads up very fast! What host are you using? Can I get your affiliate link to your host? I wish my website loaded up as quickly as yours lol

Thank you for your generous feedback! I’m glad you find the site fast and enjoyable. I don’t have affiliate links or specific hosting details to share.

Thanks for the sensible critique. Me & my neighbor were just preparing to do some research about this. We got a grab a book from our area library but I think I learned more clear from this post. I am very glad to see such magnificent information being shared freely out there.

Thank you so much! I’m delighted this post helped clarify things for you and your neighbor. I truly appreciate your kind words and support.