Contents

1. JFET 란?

Junction Field Effect Transistor (JFET)는 전자의 흐름을 제어하기 위해 역방향 바이어스 pn-접합에서의 전기장을 이용하는 유니폴라 장치입니다.

JFET 동작 원리는 두 개의 전극 사이에서의 전류 흐름을 이 전기장의 작용에 의해 제어하며, 이는 전자의 움직임을 조절하여 전류의 흐름을 변화시킵니다.

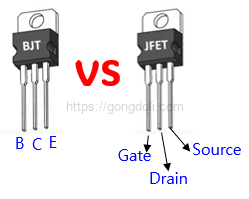

일반적으로 바이폴라 접합 트랜지스터(BJT)는 트랜지스터의 출력인 콜렉터 전류가 베이스 단자로 흐르는 입력 전류와 비례한다는 것을 알고 있을 것입니다.

이는 바이폴라 트랜지스터를 “전류”를 제어하는 장치로 만들어주며, 더 작은 입력 전류로도 더 큰 부하 전류를 전환할 수 있도록 합니다.

그러나 JFET 동작 원리는 입력 단자에 가해진 전압, 즉 게이트 전압을 사용하여 전류를 제어합니다.

이는 게이트에 가해지는 전압에 따라 전자의 흐름을 변화시키는 방식으로 작동하며, 이렇게 변화된 전자의 흐름에 따라 출력 전류가 입력 전압에 비례하게 됩니다.

즉, JFET 동작 원리을 이용하여 게이트와 소스 간의 전압을 조절하여 소스와 드레인 간의 전류를 제어합니다.

그리고 이러한 동작 방식은 전압에 의해 제어되기 때문에 전계 효과 트랜지스터를 “전압”으로 작동하는 장치로 만듭니다.

전계 효과 트랜지스터는 바이폴라 트랜지스터와 매우 유사한 성능을 가진 세 개의 단자 유니폴라 반도체 장치입니다.

이러한 트랜지스터는 바이폴라 트랜지스터의 다양한 장점을 가지고 있으며, 고효율, 즉시 작동, 견고하고 저렴하며 대부분의 전자 회로 응용 분야에서 바이폴라 접합 트랜지스터 (BJT)를 대체할 수 있습니다.

FET 동작 원리로 인해 동등한 BJT 트랜지스터보다 훨씬 작게 만들 수 있습니다.

이러한 특성은 통합 회로에 이상적으로 사용될 수 있으며, 저전력 소비와 저전력 소비는 CMOS 범위의 디지털 논리 칩과 같은 곳에서 특히 중요합니다.

또한 전계 효과 트랜지스터는 N채널 FET와 P채널 FET 두 가지 기본 분류로 나뉩니다.

이는 바이폴라 트랜지스터의 NPN 및 PNP와 유사한 개념입니다.

N채널 FET는 전류의 흐름을 전자의 전도에 의존하여 제어하고, P채널 FET는 홀의 전도에 의존하여 제어합니다.

FET는 주된 전류 경로인 드레인과 소스 터미널 사이에 PN 접합이 없이 구성된 세 단자 장치입니다.

이는 바이폴라 트랜지스터의 콜렉터와 에미터에 해당합니다.

이 두 터미널 사이의 전류 경로를 “채널”이라고하며 P-유형 또는 N-유형 반도체 재료 중 하나로 제작될 수 있습니다.

FET의 게이트에 적용되는 전압을 조절하여 채널에서 흐르는 전류를 제어합니다.

따라서 FET는 전압으로 작동되는 장치로, 입력 전압의 변화에 따라 출력 전류가 변화합니다.

이러한 특성은 전계 효과 트랜지스터를 전압으로 작동하는 장치로 만듭니다.

FET에는 주로 두 가지 주요 유형이 있습니다.

하나는 Junction Field Effect Transistor(JFET)이며, 다른 하나는 Insulated-gate Field Effect Transistor(IGFET)입니다.

JFET 동작 원리는 pn-접합을 이용하여 전류를 제어하며, IGFET(MOSFET) 동작 원리는 게이트와 채널 사이에 절연층을 가지고 있어 게이트 전압을 조절함으로써 전류를 제어합니다.

- 연관 참조 : NPN이란?, NPN 트랜지스터 동작 원리, 구성, 예제 2문제, 장.단점

- 연관 참조 : PNP 트랜지스터 원리, 심볼, 구성, 회로, 단자 저항값 비교

- 연관 참조 : 트랜지스터 스위칭 회로,동작 원리, NPN, PNP 스위칭 회로,예제2, 달링턴 회로,설계 주의

- 연관 참조 : MOSFET 동작 원리, 트랜지스터 분류,구조, N-ch 동작 원리,특성

- 연관 참조 : MOSFET 스위칭 회로,동작 원리,LED 제어,예제1과RDS(on)값이 중요한 이유,모터 제어

2. JFET 심볼 및 구조

2-1) JFET 심볼

- 바이폴라 트랜지스터 (Bipolar Transistor)

NPN 및 PNP 바이폴라 트랜지스터는 각각 세 개의 연결된 화살표가 있는 회로 기호를 가지고 있습니다.

NPN 바이폴라 트랜지스터의 경우 화살표는 베이스에서 에미터로 향합니다.

PNP 바이폴라 트랜지스터의 경우 화살표는 에미터에서 베이스로 향합니다. - JFET (Junction Field-Effect Transistor)

JFET는 N채널 및 P채널의 두 가지 유형이 있으며 각각 다른 회로 기호를 가집니다.

N채널 JFET의 회로 기호는 화살표가 드레인 또는 소스에서 게이트 쪽을 향합니다.

P채널 JFET의 회로 기호는 화살표가 게이트 쪽에서 드레인 또는 소스 채널을 향합니다.

이러한 차이점은 각 바이폴라 트랜지스터와 JFET 동작 원리를 나타내며, 회로에서 적절한 트랜지스터를 식별하는 데 도움이 됩니다.

2-2) JFET 구조(N type)

N형 JFET(접합장 효과 트랜지스터)는 일반적으로 세 개의 주요 요소로 구성됩니다

게이트(Gate), 드레인(Drain), 그리고 소스(Source). 이들 요소는 N형 기판(N-type substrate)에서 만들어집니다.

- 게이트(Gate): N형 JFET의 게이트는 기본적으로 P형 물질로 만들어진다.

게이트는 채널을 제어하는데 사용되며, 게이트 전압이 증가하면 채널의 전도도가 감소하고, 게이트 전압이 감소하면 채널의 전도도가 증가합니다. - 드레인(Drain): 드레인은 JFET의 출력 단자로 동작합니다.

전자는 소스에서 드레인까지 이동하며, 게이트 전압에 따라 소스와 드레인 사이의 채널 전도도가 변화합니다. - 소스(Source): 소스는 전자의 출발 지점으로 작동합니다.

게이트의 전압에 따라 소스와 드레인 사이의 채널 전도도가 변화하고, 이는 출력 전류에 영향을 미칩니다. - N형 기판(N-type substrate): N형 JFET의 기판은 N형 반도체 재료로 만들어집니다.

이 기판은 전체 장치를 지지하고 안정성을 제공합니다. - P형 물질(P-type material): 게이트를 형성하는 P형 물질은 전압을 제어하여 소스와 드레인 사이의 채널을 형성하고 전도도를 조절합니다.

3. JFET 동작 원리

FET는 게이트(Gate), 소스(Source), 그리고 드레인(Drain)이라는 세 개의 전극을 가지고 있는 반도체 장치입니다.

이 중에서도 JFET 동작 원리를 이용하여 pn-접합의 역방향 전압에 따라 게이트와 소스 사이의 전류 흐름을 제어합니다.

JFET 동작 원리 핵심은 채널의 효과적인 단면적입니다.

채널은 소스와 드레인 사이의 반도체 영역을 의미합니다.

게이트에 가해지는 전압이 변화하면 채널의 전도도가 변화하게 되어 전류의 흐름을 제어합니다.

이것이 JFET 동작 원리입니다.

예를 들어, 게이트에 전압이 가해지지 않은 상태에서는 JFET의 채널이 전혀 형성되지 않습니다.

이러한 상황에서는 전류가 흐르지 않습니다.

하지만 게이트에 양수 전압이 가해지면 채널이 형성되어 소스에서 드레인으로 전류가 흐르게 됩니다.

따라서 JFET는 입력 전압에 따라 출력 전류를 제어할 수 있는 장치입니다.

이러한 특성은 FET를 “전압”으로 동작하는 장치로 만듭니다.

이러한 FET의 높은 입력 임피던스는 입력 전압 신호에 매우 민감하게 반응하지만, 높은 민감도는 정전기에 의해 쉽게 손상될 수 있다는 것을 의미합니다.

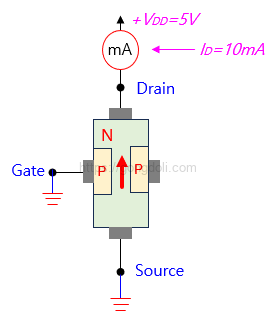

3-1) JFET가 게이트 바이어스가 없는 상태

제로 게이트 바이어스에서 JFET가 작동하는 경우, 게이트 터미널에 외부 전압이 적용되지 않는 것을 의미합니다.

이 조건에서 JFET는 기본 상태에서 동작하며, 채널 전도도는 소스와 드레인 터미널 사이의 전압에만 의해 결정됩니다.

그림은 JFET(정류장 Field Effect Transistor)이 게이트 바이어스가 없는 조건에서 어떻게 동작하는지를 보여줍니다.

JFET에 5V 전압이 가해지면 전자 전류가 소스에서 드레인으로 향하게 됩니다.

이것은 소스와 드레인 사이의 전류 흐름을 나타내는 화살표로 나타냅니다.

이때 게이트 터미널은 접지에 연결되어 있으며, 이것이 바로 게이트 바이어스가 없는 조건입니다.

게이트 바이어스가 없는 상태에서는 전형적으로 채널이 약 500 Ω의 저항을 가지고 있습니다.

이는 전류가 흐르는데 제한을 가하는 저항입니다.

드레인과 DC 전원에 직렬로 연결된 mA메타는 전류의 양을 측정합니다.

5V의 드레인 공급 전압 (VDD)으로, mA메타는 드레인 전류 (ID)가 10 mA가 나오게 됩니다.

이와 같은 전류 및 전압 측정값은 FET의 요소에 대한 특정 변수를 나타내는 데 사용됩니다.

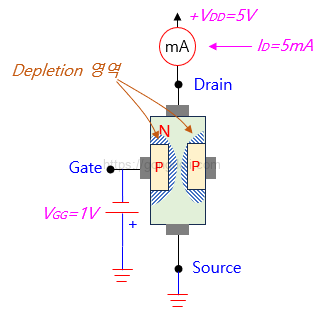

3-2) JFET의 게이트에 소량의 역바이어스 전압이 인가 상태

아래 그림에서는 JFET의 게이트에 소량의 역 바이어스 전압이 인가됩니다.

이렇게 되면 P-유형 게이트 물질과 N-유형 물질 사이의 결합이 역 바이어스 상태가 됩니다.

역 바이어스 상태에서는 PN 접합 주변에 “소진 영역”이 형성됩니다.

이 소진 영역은 전류 이동체의 수가 감소하므로, 채널의 유효 단면적이 줄어들게 됩니다.

결과적으로 장치의 소스-드레인 저항이 증가하고 전류 흐름이 감소합니다.

이러한 JFET 동작 원리로 게이트에 인가된 전압의 변화에 따라 JFET의 채널 크기가 조절되며, 따라서 장치의 전류 흐름이 제어됩니다.

3-3) JFET의 게이트에 큰 Negative 전압을 인가

게이트에 충분히 큰 음 전압을 가하면 소진 영역이 커져서 막대를 통한 전류 이동이 완전히 차단됩니다.

이 전압이 필요한 양을 소진 전압(또는 한계 전압)이라 하며, 이것은 진공관의 차단 전압과 유사합니다.

위의 그림에서 음수 1V가 적용되었지만 전류가 완전히 차단되지는 않았으며, 결과적으로 드레인 전류가 상당히 감소했습니다(게이트 바이어스가 없을 때 10mA에서 5mA로).

이러한 전압이 JFET의 전체 저항을 증가시켰습니다(500Ω에서 1kΩ으로).

다시 말해, 게이트 전압의 1V 변화가 장치의 저항을 두 배로 증가시키고 전류 흐름을 절반으로 줄였습니다.

그러나 이러한 측정 결과는 두 장치가 서로 다르게 구성되었음에도 불구하고 JFET이 바이폴라 트랜지스터와 유사한 방식으로 동작한다는 것을 보여줍니다.

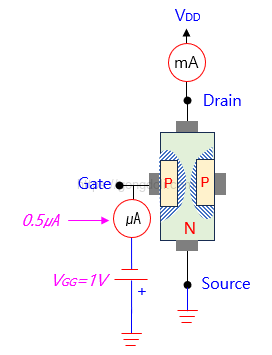

앞서 언급한 바와 같이, FET의 주요 장점은 입력 임피던스가 바이폴라 트랜지스터보다 훨씬 높다는 것입니다.

VGG가 1V인 경우, ㎂메터는 0.5㎂를 표시합니다.

오옴의 법칙을 적용하면 (1V / 0.5µA), 이 매우 작은 전류 흐름이 매우 높은 입력 임피던스를 유발한다는 것을 보여줍니다(약 2MΩ).

이에 비해 유사한 상황에서 바이폴라 트랜지스터는 더 높은 전류 흐름(예: 0.1에서 1mA)이 필요하며, 결과적으로 훨씬 낮은 입력 임피던스(약 1000Ω 이하)가 됩니다.

JFET의 높은 입력 임피던스는 역방향 바이어스 게이트 전압이 채널의 단면적에 어떻게 영향을 미치는지 때문에 가능합니다.

4. JFET의 출력특성 V-I 곡선

4-1) JFET 출력 특성 곡선

JFET 동작 원리에서 JFET의 출력 특성 곡선은 드레인 전압(VDS)을 x축으로, 드레인-소스 전류(ID)를 y축으로 표시합니다.

이러한 곡선은 게이트 전압(VGS)이 일정한 조건에서 변할 때 JFET 동작 원리를 보여줍니다.

- 저항(Ohmic) 영역 – VGS = 0 일 때 채널의 고갈 층이 매우 작아서 JFET가 전압 제어 저항으로 작동합니다.

이 영역에서 JFET는 게이트에 인가된 전압에 따라 선형적인 방식으로 동작합니다.

따라서 채널의 저항은 VGS와 비례하여 변화합니다. - 차단(Cut-off) 영역 – 이 영역에서는 게이트와 소스 사이의 전압이 높아서 JFET의 채널이 완전히 차단됩니다.

이것은 게이트-소스 전압 VGS가 필화 전압(VP)보다 높을 때 발생합니다.

채널은 차단되어 드레인과 소스 간에 전류가 흐르지 않게 됩니다. - 포화 또는 활성(Saturation or Active) 영역 – 이 영역에서는 JFET가 게이트에 인가된 전압에 의해 전압 제어되고 드레인과 소스 간에 전류가 흐릅니다.

채널은 완전히 활성화되어 있으며, 게이트에 인가된 전압의 변화는 드레인과 소스 간의 전류에 큰 영향을 미칩니다.

이 영역에서는 JFET가 특정한 전압 조건 아래에서 작동하며, 이 조건에서는 JFET의 전도 특성이 거의 일정합니다. - 고장(Breakdown) 영역 – 이 영역에서는 드레인과 소스 사이의 전압(VDS)이 JFET의 채널을 파괴하고 무 제어 최대 전류가 흐르게 됩니다.

이것은 JFET가 과부하되어 전원을 통과시키지 않는 안정된 작동 영역을 벗어나게 될 때 발생합니다.

이것은 일반적으로 JFET의 정상 동작 영역을 벗어난 경우에만 발생하는 문제입니다.

4-2) 활성 영역의 Drain 전류

JFET 동작 원리에서 활성 영역에서의 드레인 전류는 주로 게이트-소스 전압(VGS)에 의해 제어되며 드레인-소스 전압(VDS)의 영향을 거의 받지 않습니다.

이 영역에서 JFET는 전압 제어 전류원으로 동작합니다.

드레인 전류와 게이트-소스 전압 간의 관계는 다음과 같은 방정식으로 근사될 수 있습니다.

- 여기서

- ID 는 드레인 전류입니다.

- IDSS 는 VGS=0 일 때 최대 드레인 전류이며 드레인-소스 포화 전류로도 알려져 있습니다.

- VGS 는 게이트-소스 전압입니다.

- VP 는 핀치오프 전압입니다.

활성 영역에서는

- VGS=0 일 때 드레인 전류는 최대값인 IDSS 입니다.

- VGS 가 보다 음수가 되면 드레인 전류가 감소하며 핀치오프 전압 (VP) 에서 0에 가까워집니다.

- VGS 를 변화시킴으로써 드레인 전류를 다양하게 제어할 수 있습니다.

이 관계는 JFET의 활성 영역에서 게이트-소스 전압을 조절함으로써 드레인 전류를 변조할 수 있음을 보여주며, 이는 JFET 동작 원리를 이용하여 다양한 전압 제어 응용에 적합하게 만듭니다.

이러한 출력 특성 곡선은 JFET 동작 원리를 이해하고 설계할 때 중요한 참고 자료입니다.

JFET의 특성을 정확히 이해하려면 이러한 곡선을 분석하고 해석하는 것이 필요합니다.

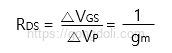

4-3) Drain-Source Channel 저항

JFET 동작 원리 중 드레인-소스 채널 저항은 JFET의 활성 영역에서 중요한 매개 변수 중 하나입니다.

이 저항은 드레인 전류와 드레인-소스 전압 간의 관계를 설명하는 중요한 요소입니다.

활성 영역에서 드레인-소스 채널 저항은 일정한 전압을 유지하고 일정한 드레인 전류를 유지할 때 변화합니다.

일반적으로 JFET의 활성 영역에서 드레인-소스 채널 저항은 다음과 같이 근사될 수 있습니다.

- 여기서

gm은 “transconductance gain”이며 JFET가 전압 제어 장치이기 때문에 게이트-소스 전압의 변화에 대한 드레인 전류의 변화율을 나타냅니다

You are my breathing in, I have few blogs and often run out from to post .

Thank you

Admiring the commitment you put into your website and in depth information you present. It’s good to come across a blog every once in a while that isn’t the same unwanted rehashed information. Great read! I’ve saved your site and I’m adding your RSS feeds to my Google account.

Thank you so much for your kind words and support!

I was very pleased to find this web-site.I wanted to thanks for your time for this wonderful read!! I definitely enjoying every little bit of it and I have you bookmarked to check out new stuff you blog post.

Thank you so much—that really means a lot!

I’m thrilled to hear you’ve been enjoying the blog, and I truly appreciate the bookmark.

Real fantastic information can be found on web blog.

I’m so glad you found the blog helpful!

It’s always rewarding to know that the information shared is making a real impact.

Great line up. We will be linking to this great article on our site. Keep up the good writing.

Thank you so much for your support!

I’m honored that you’ll be linking to the article

You should take part in a contest for one of the best blogs on the web. I will recommend this site!

That’s incredibly kind—thanks so much for the recommendation!

Fantastic site. Plenty of useful information here. I am sending it to several friends ans also sharing in delicious. And obviously, thanks for your sweat!

Thank you so much!

I truly appreciate your support and sharing.

I am perpetually thought about this, regards for posting.

Thank you very much!

Very nice article and right to the point. I don’t know if this is really the best place to ask but do you people have any thoughts on where to hire some professional writers? Thanks in advance 🙂

Thank you! I’m glad you enjoyed the article.

Thanks , I have recently been looking for information approximately this topic for ages and yours is the best I’ve came upon so far. However, what about the conclusion? Are you certain about the supply?

Thank you for your thoughtful feedback.

Your writing style makes even technical topics accessible and engaging without oversimplifying important details. I appreciate how you balanced depth with readability throughout the article. This is exactly the kind of content that helps bridge the gap between specialists and general audiences.

Thank you for your thoughtful feedback.

My brother suggested I might like this web site. He was totally right. This post actually made my day. You cann’t imagine simply how much time I had spent for this info! Thanks!

Thank you so much! I’m truly glad this post made your day and that the information was helpful.