1. MOSFET 파손 원인은?

MOSFET 파손의 주요 원인은 다양한 과정을 통해 발생할 수 있습니다.

먼저, 안전 작동 영역(SOA)을 초과하는 경우, MOSFET 파손은 과전압이나 과전류에 의해 생길 수 있습니다.

이는 전원 회로의 오버로드나 단락으로 인한 상황에서 발생할 수 있습니다.

또한, Avalanche Breakdown은 MOSFET 파손의 일반적인 원인 중 하나입니다.

이는 고전압 상태에서 PN 접합이 역방향 전압에 의해 역전파되면서 발생합니다.

또한, dV/dt에 의한 MOSFET 파손은 MOSFET이 고주파 또는 고속 전압 변화에 민감할 때 발생합니다.

이러한 변화는 MOSFET의 게이트와 드레인 사이에 발생하는 전위 차이에 의해 결정됩니다.

모든 이러한 요인들은 MOSFET 파손을 초래할 수 있으며, 적절한 회로 설계와 보호 회로의 구현이 중요합니다.

- 연관 참조 : NPN이란?, NPN 트랜지스터 동작 원리, 구성, 예제 2문제, 장.단점

- 연관 참조 : PNP 트랜지스터 원리, 심볼, 구성, 회로, 단자 저항값 비교

- 연관 참조 : 트랜지스터 스위칭 회로,동작 원리, NPN, PNP 스위칭 회로,예제2, 달링턴 회로,설계 주의

- 연관 참조 : JFET 동작 원리,심볼,구조,출력 특성 곡선(V-I)

- 연관 참조 : MOSFET 동작 원리, 트랜지스터 분류,구조, N-ch 동작 원리,특성

2. SOA (Safety Operation Area) 파손

SOA는 Safety Operation Area의 약자로, 반도체 장치인 MOSFET 등이 안전하게 동작할 수 있는 전압과 전류의 범위를 나타냅니다.

MOSFET이나 다른 반도체는 이 SOA 범위 내에서만 안전하게 사용할 수 있습니다.

즉, 특정한 전압과 전류의 조합이 이 범위를 벗어나면 장치가 손상될 수 있습니다.

SOA를 제한하는 5가지 요건 중 하나라도 초과하게 되면, MOSFET 파손될 가능성이 있습니다.

2-1) SOA (Safety Operation Area)란?

SOA(Safe Operating Area)는 반도체 장치인 MOSFET 등이 안전하게 동작할 수 있는 전압과 전류의 범위를 나타냅니다.

이는 장치가 오버전압, 과전류 또는 과열로부터 손상을 보호하는 중요한 개념입니다.

SOA는 MOSFET이나 다른 반도체 장치가 어느 정도의 전압과 전류에서 안전하게 동작할 수 있는지를 정량적으로 나타냅니다.

따라서 SOA를 벗어나는 조건에서 장치를 사용하면 파손될 수 있으므로, 설계 과정에서 이러한 조건을 엄격하게 고려해야 합니다.

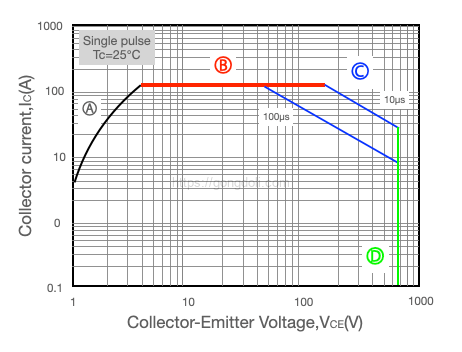

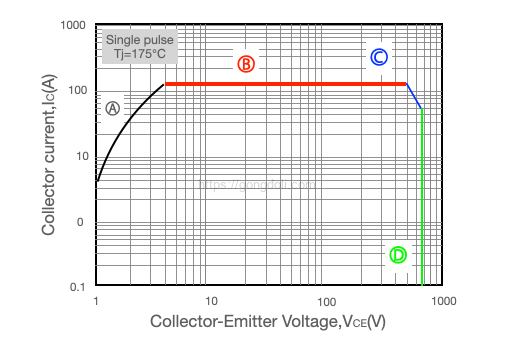

2-2) 순방향 바이어스 SOA (Forward Bias Safe Operating Area,FBSOA)

순방향 바이어스 안전 작동 영역(FBSOA)은 IGBT가 켜지는 동안 손상이나 파손 없이 사용될 수 있는 전류와 전압의 범위를 나타냅니다.

순방향 바이어스 안전 작동 영역은 다음과 같은 제한으로 나누어집니다.

Ⓐ 콜렉터-에미터 포화 전압인 VCE(SAT)로 제한되는 영역

Ⓑ 최대 정격값인 콜렉터 전류로 제한되는 영역

Ⓒ 최대 정격값인 접합 온도로 제한되는 영역(열적 제한 영역)

Ⓓ 콜렉터-에미터 전압인 VCE의 최대 정격값으로 제한되는 영역

2-3) 역방향 바이어스 SOA(Reverse Bias Safe Operating Area, RBSOA)

역방향 바이어스 안전 작동 영역(RBSOA)은 다이오드 또는 다이오드를 포함하는 반도체 장치가 역방향 전압에 노출되어도 손상되거나 파손되지 않고 동작할 수 있는 범위를 나타냅니다.

RBSOA는 역방향 전압이 적용된 상황에서 반도체 장치가 안전하게 동작하는 범위를 나타냅니다.

역방향 바이어스 안전 작동 영역은 다음과 같은 제한으로 나누어집니다.

Ⓐ 콜렉터-에미터 포화 전압인 VCE(SAT)로 제한되는 영역

Ⓑ 최대 정격 최대 피크 값인 콜렉터 전류로 제한되는 영역

Ⓒ IGBT에 특정한 특성으로 제한되는 영역

Ⓓ 콜렉터-에미터 전압인 VCE의 최대 정격값으로 제한되는 영역

2-4) SOA의 각 영역과 제한 및 파손과의 관계

■ 영역 Ⓐ : MOSFET의 ON 저항 RDS(ON)에 의해 드레인 전류 ID가 제한되는 영역

이 영역은 MOSFET의 채널 내 저항인 RDS(ON)에 의해 결정됩니다.

이 영역에서는 인가된 VDS가 최대 정격 이하이더라도 RDS(ON)에 의해 ID가 제한됩니다.

■ 영역 Ⓑ : 펄스 인가 시 드레인 전류의 절대 최대 정격 IDP에 의해 결정되는 영역

적색 선은 사양서에 기재된 절대 최대 정격 IDP의 값입니다.

이 값을 초과하는 영역에서는 동작 보증 범위를 벗어나므로 MOSFET 파손의 우려가 있습니다.

■ 영역 Ⓒ : 열 제한 영역/2차 항복 영역

이 영역은 MOSFET의 허용 손실 PD에 의해 결정됩니다.

이 영역에 포함된다면 일반적으로 절대 최대 정격 TjMAX를 초과하지 않으므로 안전하게 사용할 수 있습니다.

고전압 인가 상태에서 소자 내에 국소적으로 대전류가 흐르면 파손되는 경우가 있으며, 이러한 현상을 2차 항복이라고 합니다.

이 영역은 이를 피하기 위한 제한 라인입니다.

■ 영역 Ⓓ : MOSFET의 드레인 – 소스 전압의 절대 최대 정격 VDSS에 의해 결정되는 영역

이 영역을 초과하면 브레이크 다운이 발생하여 MOSFET 파손의 원인이 될 수 있습니다.

순간적으로 이 영역을 초과할 가능성이 있으므로 주의가 필요합니다.

3. Avalanche 파손

3-1) Avalanche 항복이란?

Avalanche 항복은 MOSFET이나 다이오드와 같은 반도체 소자에서 발생하는 중요한 현상 중 하나입니다.

이는 절대 최대 정격 BVDSS를 초과하는 고전압이 소자에 인가될 때 MOSFET 파손이 발생합니다.

고전압이 MOSFET의 게이트와 소스 사이에 인가되면, 이를 통해 소자 내부의 pn 접합에 역방향 전압이 생성됩니다.

이 역방향 전압은 소자의 내부 다이오드를 활성화시키고, 전류가 역방향으로 흐르게 됩니다.

이러한 역방향 전류가 MOSFET의 내부에서 충분한 에너지를 발생시키면, 이온화된 전자와 정공이 발생합니다.

이들이 충돌하고 재배열되는 과정에서, 전자와 정공의 수가 급격하게 증가하면서 전류가 폭증하게 됩니다.

이러한 현상이 눈사태의 원리와 유사하게 확산되면, Avalanche 항복이 발생하게 됩니다.

Avalanche 항복 시 MOSFET의 내부 다이오드에 대해 역방향으로 흐르는 전류를 Avalanche 전류 IAS라고 합니다.

Avalanche 항복은 소자의 파손을 초래할 수 있지만, 어떤 경우에는 이를 활용하여 원하는 특성을 얻을 수도 있습니다.

예를 들어, Zener 다이오드는 Avalanche 항복을 이용하여 특정 전압을 유지하는 데 사용될 수 있습니다.

3-2) Avalanche 파손 : short 파손

Avalanche 파손은 반도체 소자에서 주로 발생하는 파손 메커니즘 중 하나로, 고전압이 인가될 때 발생합니다.

이는 일반적으로 쇼트 파손의 한 형태입니다.

Avalanche 파손은 고전압이 소자의 pn 접합에 인가될 때 발생합니다.

이 고전압은 소자 내부의 다이오드를 활성화시키고, 역방향 전류가 흐르게 만듭니다.

이러한 역방향 전류가 충분한 에너지를 얻으면, 전자와 정공이 생성되고 충돌하면서 전류가 급증하게 됩니다.

이는 소자의 파손을 초래할 수 있으며, 전류가 폭증하여 소자의 내부에서 열이 발생하고 쇼트가 발생할 수 있습니다.

Avalanche 파손은 주로 다이오드나 MOSFET과 같은 반도체 소자에서 발생하며, 고전압이나 고에너지 펄스가 인가될 때 발생할 수 있습니다.

이러한 파손은 소자의 안전한 운영을 위해 고려되어야 하며, 적절한 보호 회로나 설계 방법을 통해 최소화할 수 있습니다.

3-3) Avalanche 파손 : 열적 파손

Avalanche 파손의 또 다른 형태는 열적 파손입니다.

이는 반도체 소자에서 발생하는 파손 메커니즘 중 하나로, 고전압이 인가될 때 발생합니다.

고전압이 MOSFET이나 다이오드와 같은 반도체 소자에 인가되면, 소자 내부에서 역방향 전류가 발생합니다.

이 역방향 전류는 소자 내부의 pn 접합에 대한 에너지를 생성하고, 이러한 과정에서 열이 발생합니다.

역방향 전류가 충분한 에너지를 얻으면, 전자와 정공이 생성되고 충돌하면서 전류가 급증하게 됩니다.

이는 소자 내부에서 열이 발생하고, 이 열이 소자의 구조를 손상시키거나 파손할 수 있습니다.

이러한 열적 파손은 반도체 소자가 지나치게 높은 전력이나 전류를 처리할 때 주로 발생할 수 있습니다.

열적 파손을 방지하기 위해서는 적절한 열 관리 및 냉각이 필요합니다.

또한, 소자가 작동 중에 발생하는 열에 대한 정확한 모델링과 설계를 통해 열적 파손을 최소화할 수 있습니다.

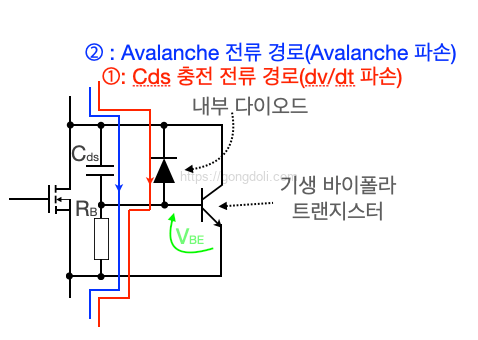

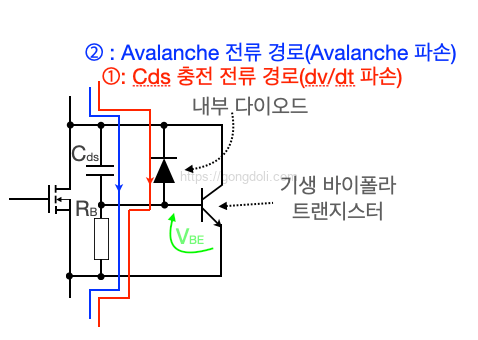

4. dv/dt 파손

4-1) dV/dt 파손이란?

dV/dt 파손은 MOSFET이나 IGBT와 같은 반도체 소자에서 주로 발생하는 파손 현상 중 하나입니다.

이는 소자가 스위칭되는 과정에서 발생하는데, 특히 소자가 turn-off될 때 주로 발생합니다.

소자가 turn-off될 때(②), 기생 용량인 Cds에 충전된 전하가 급격하게 방전되면서 발생합니다.

이는 MOSFET이나 IGBT의 경우 게이트와 소스 사이에 발생하는데, 이는 기생 바이폴라 트랜지스터(BJT)의 동작을 유도합니다.

기생 바이폴라 트랜지스터는 MOSFET이나 IGBT의 기생 구조에 내장되어 있으며, 전류가 이 트랜지스터를 통해 흐르면서 파손가 발생합니다.

dV/dt가 증가하면, 기생 바이폴라 트랜지스터의 베이스와 에미터 사이의 전압인 VBE도 증가합니다.

이 증가된 전압은 기생 바이폴라 트랜지스터를 ON 상태로 전환시키는데, 이로 인해 쇼트 파손이 발생할 수 있습니다.

이러한 현상은 dV/dt가 빠를수록 더 쉽게 발생하며, 따라서 소자의 스위칭 속도를 제어하고 적절한 보호 회로를 구현하여 이를 방지해야 합니다.

dV/dt 파손은 소자의 스위칭 작업 중에 주로 발생하는데, 특히 MOSFET이나 IGBT가 turn-off될 때 주로 발생합니다.

이때, 소자 내부의 기생 용량인 Cds에 충전된 전하가 급격하게 방전되면서 발생합니다.

이러한 기생 용량의 급격한 방전은 기생 바이폴라 트랜지스터(BJT)의 작동을 유도합니다.

MOSFET이나 IGBT 소자는 이러한 기생 바이폴라 트랜지스터를 내부에 포함하고 있습니다.

이후, 기생 바이폴라 트랜지스터의 작동으로 인해 전류가 급증하게 되는데, 이는 쇼트로 인한 MOSFET 파손의 원인이 됩니다.

dV/dt가 증가함에 따라, 기생 바이폴라 트랜지스터의 베이스와 에미터 사이의 전압인 VBE도 증가하게 됩니다.

이렇게 증가된 전압은 기생 바이폴라 트랜지스터를 ON 상태로 전환시키는데, 이로 인해 쇼트로 인한 MOSFET 파손이 발생할 수 있습니다.

즉, dV/dt 파손은 소자의 스위칭 속도가 빠를수록 더 쉽게 발생하며, 이를 방지하기 위해서는 적절한 스위칭 회로의 설계와 보호 회로의 구현이 필요합니다.

또한, 소자의 스위칭 속도를 제어하여 MOSFET 파손을 방지할 수 있습니다.

Youre so cool! I dont suppose Ive learn anything like this before. So nice to seek out anyone with some authentic ideas on this subject. realy thank you for beginning this up. this website is something that’s wanted on the net, someone with somewhat originality. useful job for bringing one thing new to the web!

Thank you so much for your amazing feedback! I’m thrilled you found the ideas refreshing. Your support truly means a lot!

It’s a shame you don’t have a donate button! I’d definitely donate to this brilliant blog! I guess for now i’ll settle for book-marking and adding your RSS feed to my Google account. I look forward to new updates and will share this site with my Facebook group. Talk soon!

Thank you so much for your generous thoughts and support! It’s truly wonderful to hear that you find the blog valuable enough to share and bookmark.

I don’t ordinarily comment but I gotta tell thanks for the post on this amazing one : D.

I truly appreciate you taking the time to leave a comment!

I like this site very much so much superb info .

Thank you so much!

Great V I should definitely pronounce, impressed with your site. I had no trouble navigating through all the tabs as well as related info ended up being truly simple to do to access. I recently found what I hoped for before you know it at all. Quite unusual. Is likely to appreciate it for those who add forums or something, web site theme . a tones way for your customer to communicate. Nice task..

Thank you—I’m glad the site was easy to use.

Very interesting topic, appreciate it for posting.

Thank you so much for your kind words.

I gotta favorite this site it seems invaluable very beneficial

Thank you! I’m glad you find the site invaluable and beneficial.

I have been browsing online greater than three hours nowadays, yet I by no means discovered any attention-grabbing article like yours. It’s lovely worth enough for me. Personally, if all web owners and bloggers made excellent content as you probably did, the internet can be a lot more useful than ever before. “We are not retreating – we are advancing in another Direction.” by Douglas MacArthur.

Thank you for your generous words. I’m glad the article was valuable

I am not rattling fantastic with English but I get hold this really easy to read .

Thank you so much! I’m glad the writing felt easy to read and accessible — that means a lot to me.

I am not sure where you are getting your information, but good topic. I needs to spend some time learning much more or understanding more. Thanks for excellent information I was looking for this information for my mission.

Thank you for your thoughtful comment.

The information is based on practical experience and reliable technical references.