Contents

1. NAND 게이트란 무엇인가?

NAND 게이트 회로는 디지털 회로 설계에서 가장 기본적이고 중요한 논리 게이트 중 하나입니다.

“NAND”는 “Not AND”의 약자로, 이는 AND 게이트의 출력을 반전시킨 결과를 의미합니다.

NAND 게이트 회로는 단순하면서도 강력한 기능을 가지고 있어 다양한 논리 회로에서 사용됩니다.

1-1) NAND 게이트의 정의

NAND 게이트 회로는 AND 게이트의 출력을 뒤집는, 즉 논리값을 반전시키는 역할을 합니다.

두 개 이상의 입력이 모두 HIGH(1)인 경우를 제외하고, 모든 입력 조합에 대해 HIGH 출력을 생성합니다.

이를 통해 NAND 게이트회로는 매우 중요한 논리 연산을 수행하며, 기본 논리 연산과 복잡한 회로 구현 모두에 사용될 수 있습니다.

간단히 말해서, NAND 게이트 회로는 AND 게이트의 결과를 반전한 논리 게이트입니다.

모든 입력이 1인 경우를 제외하고는 항상 출력이 1이 됩니다.

1-2) NAND 게이트 회로의 기본 원리

NAND 게이트의 동작 원리는 입력된 모든 값이 HIGH(1)일 때만 LOW(0) 출력을 내고, 그 외의 모든 경우에는 HIGH(1) 출력을 내는 것입니다.

이 원리는 AND 게이트의 출력을 NOT 게이트에 입력한 것과 같습니다.

따라서 NAND 게이트 회로의 출력을 구하려면 먼저 AND 연산을 수행하고, 그 결과를 반전시키면 됩니다.

AND 게이트와 NOT 게이트를 조합하여 NAND 게이트를 만들 수 있습니다.

예를 들어, 두 입력 A와 B가 주어졌을 때

- AND 게이트는 A와 B가 모두 1일 때만 1을 출력합니다.

- NOT 게이트는 이 AND 게이트의 출력을 반전시켜, A와 B가 모두 1일 때 0을 출력하고, 그 외의 경우에는 1을 출력합니다.

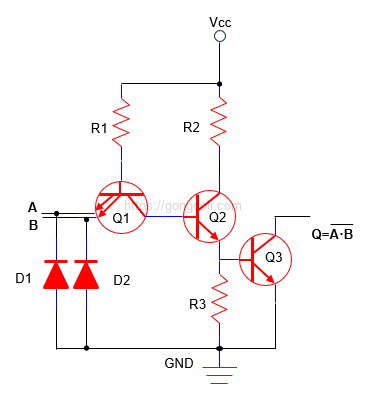

이를 수식으로 표현하면 다음과 같습니다.

1-3) NAND 게이트의 진리표와 심볼

NAND 게이트 회로 심볼은 AND 게이트와 비슷하지만, 출력 부분에 작은 원이 추가된 형태입니다.

이 원은 출력을 반전시키는 것을 나타냅니다.

이 진리표에서 볼 수 있듯이, 두 입력이 모두 1인 경우에만 출력이 0이고, 그 외의 경우에는 항상 1입니다.

이는 NAND 게이트가 모든 경우에 대해 AND 연산의 결과를 반전함을 보여줍니다.

NAND 게이트 회로는 디지털 논리 회로에서 매우 중요한 역할을 합니다.

이는 모든 입력이 1일 때만 0을 출력하고, 그 외에는 항상 1을 출력하는 특성을 가지고 있습니다.

AND 게이트와 NOT 게이트의 조합으로 구성된 NAND 게이트는 복잡한 논리 회로를 설계하는 데 필수적인 요소로, 다양한 디지털 시스템에서 핵심적으로 사용됩니다.

NAND 게이트 회로는 이러한 이유로 디지털 설계에서 자주 사용되는 중요한 구성 요소입니다.

- 연관 참조 : 디지털 논리 게이트, 입.출력, 논리 상태와 전압 레벨

- 연관 참조 : AND 게이트 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : OR 게이트 논리 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : NOT 게이트 논리 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : NOR 게이트 회로, 회로 구성, 특성 및 성능, 장점 3개와 한계

- 연관 참조 : XOR 게이트 회로 설계, 회로 구성, 특성 및 성능, 장점 3개와 한계

- 연관 참조 : XNOR 게이트 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : Buffer 회로 설계, 회로 설계의 기본 구성, 설계 고려 사항

2. NAND 게이트의 회로 구성

NAND 게이트 회로는 디지털 회로의 기본 빌딩 블록 중 하나로, 여러 가지 방법으로 구현될 수 있습니다.

각 구현 방식은 NAND 게이트가 사용하는 트랜지스터와 다이오드의 특성을 어떻게 활용하는지에 따라 다릅니다.

NAND 게이트 회로를 구성하는 방법에는 트랜지스터를 사용한 방법, 다이오드를 사용한 방법, 그리고 TTL과 CMOS 기술을 사용하는 방법이 있습니다.

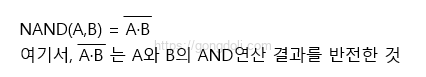

2-1) 트랜지스터를 사용한 NAND 게이트

트랜지스터를 사용한 NAND 게이트는 가장 일반적인 구현 방법 중 하나입니다.

NPN를 사용하여 NAND 게이트 회로를 구현하는 방법은 트랜지스터 두 개를 직렬로 연결하는 것입니다.

입력 신호는 트랜지스터의 베이스(기준)에 연결되고, 출력 신호는 트랜지스터의 콜렉터에서 얻어집니다.

위 그림은 두 개의 NPN 트랜지스터(T1, T2)를 사용한 NAND 게이트 회로입니다.

- 입력 A와 B : 트랜지스터 T1과 T2의 베이스에 연결됩니다.

- T1과 T2 : 직렬로 연결되어 있으며, 두 트랜지스터 모두가 활성화될 때만 출력은 LOW 상태가 됩니다.

- 출력 Q : T1의 콜렉터에서 얻어지며, 입력 중 하나라도 LOW일 때 출력은 HIGH 상태가 됩니다.

- 동작 원리 : 입력 A와 B가 모두 HIGH일 때만, T1과 T2가 모두 ON 상태가 되어, 출력은 GND(0)로 연결됩니다.

그렇지 않은 경우, 출력은 Vcc(1)로 유지됩니다.

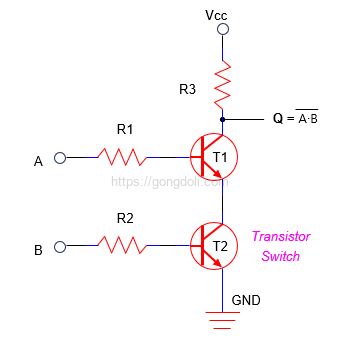

2-2) 다이오드를 사용한 NAND 게이트

다이오드를 사용한 NAND 게이트 회로는 상대적으로 간단한 회로 구성을 가집니다.

다이오드와 저항을 사용하여 NAND 연산을 구현할 수 있습니다.

다음은 다이오드를 사용한 NAND 게이트 회로입니다.

- 입력 A와 B : 다이오드 D1과 D2의 Anode에 연결됩니다.

- 다이오드 D1과 D2 : 캐소드가 공통점에서 연결되고, 이 공통점이 저항 R을 통해 Vcc에 연결됩니다.

- 출력 Q : 다이오드의 캐소드 공통점에서 얻어지며, 이는 저항을 통해 Vcc로 연결됩니다.

- 동작 원리 : 입력 A와 B가 모두 HIGH일 때, 두 다이오드가 전류를 흐르게 하여 캐소드 공통점의 전압을 낮추고, 출력은 LOW 상태가 됩니다.

입력 중 하나라도 LOW일 때, 해당 다이오드는 OFF 상태가 되어 출력은 Vcc를 유지하고 HIGH 상태가 됩니다.

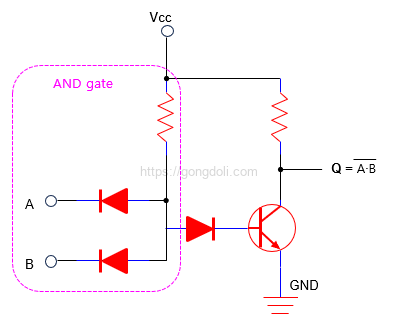

2-3) TTL 기술을 사용한 NAND 게이트

TTL 기술은 트랜지스터를 사용하여 디지털 논리 회로를 구현하는 방식입니다.

TTL NAND 게이트 회로는 여러 개의 트랜지스터와 저항으로 구성되며, 빠른 응답 속도와 비교적 높은 전력 소비가 특징입니다.

- 입력 A와 B : 트랜지스터의 에미터에 연결됩니다.

- Q1 트랜지스터는 입력에 따라 ON 또는 OFF 상태가 됩니다.

- 출력 Q : 마지막 단계 트랜지스터의 콜렉터에서 얻어집니다.

- 작동 원리: TTL NAND 게이트에서는 입력 신호가 트랜지스터를 통해 서로 결합되어 논리 연산이 수행됩니다.

일반적으로, 입력이 모두 HIGH일 때만 출력이 LOW가 되고, 나머지 경우에는 출력이 HIGH가 됩니다.

3. NAND 게이트의 특성 및 성능

3-1) 입력 및 출력 특성

NAND 게이트 회로는 디지털 논리 회로에서 중요한 역할을 하는 논리 연산자입니다.

두 개의 입력을 받아 하나의 출력을 생성하는데, 이 출력은 두 입력이 모두 LOW일 때만 HIGH가 되고, 그 외의 경우에는 항상 LOW가 됩니다. 이러한 특성은 NAND 게이트를 “부정-AND” 연산이라고도 부릅니다.

위에 진리표에서 보듯이, 두 입력 A와 B가 모두 HIGH(1)일 때만 출력 Q가 LOW(0)이 됩니다.

3-2) 게이트의 응답 시간

NAND 게이트의 응답 시간은 입력 신호가 변경된 후 출력이 변화하는 데 걸리는 시간을 의미합니다.

이 시간은 게이트가 빠르게 동작하는지를 나타내는 중요한 지표입니다.

- 응답 시간 특성

CMOS 기술에서 구현된 NAND 게이트는 일반적으로 매우 빠른 응답 시간을 가집니다.

이는 NMOS와 PMOS 트랜지스터의 상보적 동작으로 인해 입력 신호의 변화에 따라 빠르게 출력이 반응합니다.

TTL 기술의 NAND 게이트는 더욱 빠른 응답 속도를 제공할 수 있지만, 전력 소모가 높은 단점도 있습니다.

3-3) 전력 소비 특성

NAND 게이트의 전력 소비는 논리 회로가 동작하는 동안 소비하는 전력을 나타냅니다. 전력 소비는 회로의 구성 기술에 따라 다를 수 있으며, CMOS와 TTL 기술의 NAND 게이트 간에 차이가 있습니다.

- 전력 소모 특성

CMOS NAND 게이트 : CMOS 기술은 상대적으로 낮은 전력 소모를 제공합니다.

이는 NMOS와 PMOS 트랜지스터가 입력 신호가 없을 때 거의 전류를 소비하지 않기 때문입니다.

TTL NAND 게이트 : TTL 기술은 CMOS에 비해 전력 소모가 높습니다.

이는 TTL 논리 회로가 활성화된 상태에서도 상당한 전류를 소비하기 때문입니다.

- 최적화와 선택

디지털 시스템 설계에서는 전력 소모를 최소화하면서도 충분한 응답 속도를 보장해야 합니다.

이를 위해 CMOS 기술이 많이 사용되며, 특히 모바일 기기나 저전력 요구가 있는 장치에서는 CMOS NAND 게이트가 선호될 수 있습니다.

4. NAND 게이트의 장점과 한계

4-1) NAND 게이트의 주요 장점

NAND 게이트 회로는 디지털 전자 회로 설계에서 가장 널리 사용되는 기본적인 논리 게이트 중 하나입니다.

이는 여러 가지 장점 덕분에 다양한 응용 분야에서 핵심적인 역할을 합니다.

- 다양한 논리 회로 구현 가능

NAND 게이트는 다른 논리 게이트들을 포함한 다양한 논리 기능을 구현하는 데 사용될 수 있습니다.

예를 들어, AND, OR, NOT, NOR, XOR 등의 기본 논리 게이트들은 모두 NAND 게이트 조합을 통해 생성될 수 있습니다.

이를 통해 디지털 회로 설계 시, 여러 종류의 논리 게이트를 따로 사용하는 대신 NAND 게이트 하나만으로도 복잡한 논리 구조를 구현할 수 있습니다. - 상대적으로 간단한 구조

NAND 게이트는 구조적으로 간단하며, 트랜지스터를 이용해 쉽게 구현할 수 있습니다.

이는 회로의 제작과 테스트를 용이하게 합니다.

CMOS 기술에서 NAND 게이트는 NMOS와 PMOS 트랜지스터의 간단한 배열로 구성되어, 회로 설계 및 제조 시 비용 절감 효과가 있습니다. - 높은 속도와 낮은 전력 소모

CMOS 기술을 사용한 NAND 게이트는 매우 빠른 응답 시간을 제공하며, 동작 시 낮은 전력 소모를 유지합니다.

이는 특히 저전력 요구가 중요한 모바일 장치나 배터리로 구동되는 시스템에서 유리합니다.

TTL NAND 게이트는 CMOS에 비해 전력 소모가 더 크지만, 여전히 많은 디지털 시스템에서 사용될 만큼 효율적입니다. - 보편성 및 범용성

NAND 게이트는 많은 디지털 시스템의 기본 구성 요소로서, 다양한 응용 분야에서 표준적으로 사용됩니다.

이는 시스템 설계 시 부품 선택과 관련된 복잡성을 줄여줍니다.

또한, 교육적 목적으로도 많이 사용되어 디지털 논리 회로를 처음 배우는 학생들에게 핵심적인 학습 도구로 활용됩니다.

4-2) NAND 게이트의 한계와 단점

NAND 게이트 회로는 여러 가지 장점이 있지만, 몇 가지 한계와 단점도 존재합니다.

- 노이즈 면역성

NAND 게이트 회로는 노이즈에 민감할 수 있습니다.

특히 고속 스위칭 환경에서 노이즈에 의해 오동작이 발생할 수 있습니다.

이를 방지하기 위해 회로 설계 시 충분한 노이즈 여유를 고려해야 합니다. - 전력 소모

TTL NAND 게이트는 CMOS에 비해 더 많은 전력을 소비할 수 있습니다.

이는 TTL 회로가 작동 중에 지속적으로 전류를 소모하기 때문입니다.

고전력 소모는 발열 문제를 야기할 수 있으며, 이는 시스템 안정성에 영향을 미칠 수 있습니다. - 전압 레벨 제한

NAND 게이트는 특정 전압 레벨에서만 작동할 수 있습니다.

TTL NAND 게이트는 보통 5V 전원에서 작동하며, CMOS NAND 게이트는 3.3V, 5V 등 다양한 전압에서 작동할 수 있지만, 특정 전압 범위를 초과할 경우 손상될 수 있습니다.

NAND 게이트 회로는 모든 다른 논리 게이트를 구현할 수 있는 유니버설 게이트로서, 기본적인 논리 연산을 효율적으로 수행합니다.

경제성과 고속 동작의 장점을 가지고 있지만, 노이즈 민감성과 전력 소모의 한계도 존재합니다.

다른 논리 게이트와 비교할 때, NAND 게이트의 유연성과 효율성은 디지털 회로 설계에서 매우 중요한 역할을 합니다.

excellent post.Ne’er knew this, thanks for letting me know.

Thank you! I’m glad the post could provide you with new information.

This is a topic close to my heart cheers, where are your contact details though?

Thank you so much for your interest. If you have any questions, feel free to leave a comment!

Currently it seems like BlogEngine is the best blogging platform out there right now. (from what I’ve read) Is that what you’re using on your blog?

Thanks for your message!

Whats up very nice website!! Guy .. Beautiful .. Wonderful .. I will bookmark your website and take the feeds additionally…I am happy to search out numerous useful information right here in the publish, we need develop more strategies on this regard, thanks for sharing. . . . . .

Thank you so much for your enthusiastic feedback!

I’m thrilled that you found the site beautiful and informative.

It’s great to hear you’ve bookmarked it and subscribed to the feed.

You made some decent points there. I did a search on the topic and found most people will agree with your site.

Thanks for taking the time to look into it!

It’s encouraging to hear that the points made align with what others are saying too.

I really enjoy looking at on this site, it holds excellent content.

Thanks a lot! I’m glad you’re enjoying the content.

I have recently started a website, the information you provide on this site has helped me tremendously. Thank you for all of your time & work.

So glad it helped—thanks for your kind words!

Nice read, I just passed this onto a friend who was doing some research on that. And he actually bought me lunch because I found it for him smile So let me rephrase that: Thanks for lunch! “How beautiful maleness is, if it finds its right expression.” by D. H. Lawrence.

That’s a great story—glad the post came in handy, even if I’m not sure how!

We stumbled over here by a different web page and thought I should check things out. I like what I see so now i am following you. Look forward to finding out about your web page for a second time.

Thank you—I’m glad you decided to follow.

I¦ve learn a few just right stuff here. Certainly price bookmarking for revisiting. I surprise how so much attempt you set to make this sort of excellent informative web site.

I’m truly grateful for your thoughtful comment. It means a lot!

There are some fascinating points in time in this article but I don’t know if I see all of them middle to heart. There’s some validity but I will take maintain opinion till I look into it further. Good article , thanks and we wish more! Added to FeedBurner as nicely

Thank you for taking the time to read and share your thoughts. I truly appreciate your support!

You made some first rate factors there. I looked on the internet for the issue and found most people will associate with with your website.

I appreciate your thoughtful feedback. It means a lot that others find value in the site as well.

Those are yours alright! . We at least need to get these people stealing images to start blogging! They probably just did a image search and grabbed them. They look good though!

Thank you! I’m glad if this can be helpful to someone.

My brother recommended I might like this blog. He was once entirely right. This put up actually made my day. You can not believe just how a lot time I had spent for this information! Thank you!

Thank you for your kind words. I’m glad this post made your day and saved you time.

I really appreciate this post. I?¦ve been looking all over for this! Thank goodness I found it on Bing. You have made my day! Thanks again

Thank you so much! I’m delighted this post gave you the information you were searching for and brightened your day.