1. NOR 게이트 회로란 무엇인가?

NOR 게이트 회로는 디지털 논리 회로에서 매우 중요한 역할을 하는 기본적인 논리 게이트 중 하나입니다.

“NOT OR”의 약자인 NOR 게이트는 OR 게이트의 출력에 NOT 게이트를 추가하여, OR 게이트 출력의 부정(NOT)된 값을 출력하는 논리 회로입니다.

1-1) NOR 게이트의 정의

NOR 게이트는 두 개 이상의 입력 값 중 하나라도 논리적 참(1)이면, 출력이 거짓(0)이 되는 디지털 논리 회로입니다.

만약 모든 입력이 거짓(0)이면, 출력은 참(1)이 됩니다.

즉, OR 게이트의 출력 결과를 반대로 뒤집은 결과를 생성합니다.

이러한 특성으로 인해, NOR 게이트 회로는 “유니버설 게이트”로 분류되며, 단순한 조합으로 다른 모든 논리 게이트를 구현할 수 있는 장점이 있습니다.

1-2) NOR 게이트의 기본 원리

NOR 게이트 회로의 기본 원리는 다음과 같습니다.

- OR 연산 수행 : 입력 값 중 하나라도 참(1)인 경우 OR 게이트의 출력이 참(1)이 됩니다.

- NOT 연산 수행 : OR 게이트의 출력을 부정(NOT)하여, 최종 출력은 OR 게이트의 출력의 반대 값이 됩니다.

쉽게 말해서, NOR 게이트는 입력 값 중 하나라도 참(1)이 있으면, 그 결과를 부정하여 항상 거짓(0)을 출력합니다.

예를 들어, 두 입력 값이 A와 B인 경우,

NOR 게이트의 출력은

로 표현할 수 있습니다.

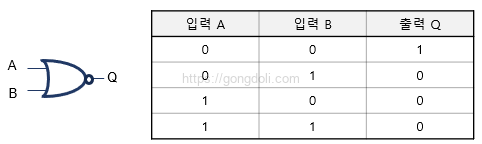

1-3) NOR 게이트의 진리표와 심볼

NOR 게이트의 동작을 이해하기 위해, 진리표와 심볼을 살펴보겠습니다.

- 진리표는 모든 가능한 입력 조합에 대한 게이트의 출력을 나타냅니다.

- 심볼은 회로 다이어그램에서 NOR 게이트를 시각적으로 나타내는 표준화된 기호입니다.

OR 게이트 심볼의 끝에 작은 원(circle)이 추가되어, OR 게이트의 출력을 부정(NOT)하는 것을 시각적으로 나타냅니다.

- 연관 참조 : 디지털 논리 게이트, 입.출력, 논리 상태와 전압 레벨

- 연관 참조 : AND 게이트 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : OR 게이트 논리 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : NOT 게이트 논리 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : NAND 게이트 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : XOR 게이트 회로 설계, 회로 구성, 특성 및 성능, 장점 3개와 한계

- 연관 참조 : XNOR 게이트 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : Buffer 회로 설계, 회로 설계의 기본 구성, 설계 고려 사항

2. NOR 게이트 회로 구성

NOR 게이트는 논리적 OR 연산의 결과를 부정(NOT)하여 출력하는 디지털 논리 게이트로, 여러 가지 방식으로 구현할 수 있습니다.

NOR 게이트는 트랜지스터, 다이오드, 그리고 다양한 반도체 기술을 사용하여 구성할 수 있으며, 각 방식은 고유한 장점과 특성을 가집니다.

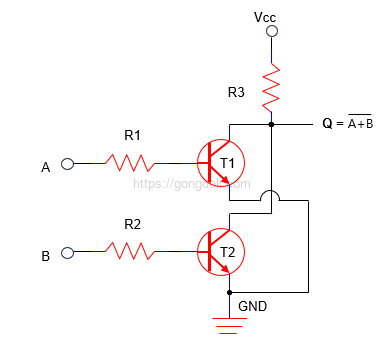

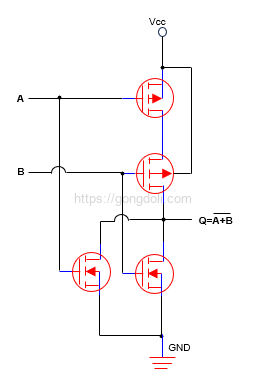

2-1) 트랜지스터를 사용한 NOR 게이트

트랜지스터는 NOR 게이트 회로를 구현하는 데 일반적으로 사용되는 기본적인 구성 요소입니다.

특히, NPN 또는 PNP 타입의 BJT(양극성 접합 트랜지스터) 또는 MOSFET(금속 산화막 반도체 전계 효과 트랜지스터)를 사용하여 NOR 게이트를 설계할 수 있습니다.

BJT를 사용한 NOR 게이트는 두 개의 NPN 트랜지스터를 사용하여 구현할 수 있습니다.

아래는 기본적인 NPN 트랜지스터를 사용한 NOR 게이트 회로입니다.

- 입력 : 트랜지스터의 베이스에 연결되어 트랜지스터의 작동 여부를 결정합니다.

- 출력 : 두 트랜지스터의 공통 컬렉터에 연결됩니다.

- 동작 원리 : 입력 신호가 0V일 때, 트랜지스터가 꺼져 있고, 출력은 Vcc(논리적 1)로 유지됩니다.

입력 중 하나라도 1V이면, 해당 트랜지스터가 켜져서 출력이 0V(논리적 0)로 됩니다.

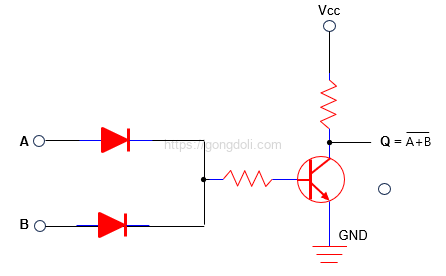

2-2) 다이오드를 사용한 NOR 게이트

다이오드 D1과 D2는 각각 A와 B의 입력을 받고, 공통 노드에서 출력이 결정됩니다.

여기서 다이오드는 반대 전압을 가하면 흐르지 않는 특성을 이용합니다.

입력 신호가 모두 0일 때 다이오드는 꺼져 있고, 풀업 저항이 출력에 Vcc를 제공합니다. 입력 중 하나라도 1이면, 해당 다이오드가 켜져서 출력이 0이 됩니다.

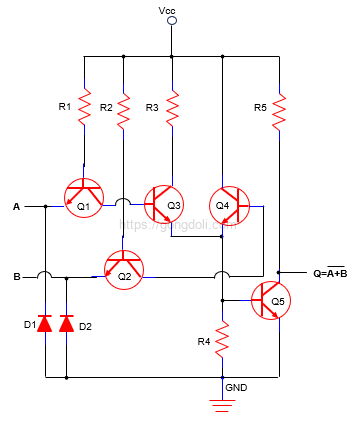

2-3) TTL 및 CMOS 기술을 사용한 NOR 게이트

NOR 게이트는 TTL(Transistor-Transistor Logic) 및 CMOS(Complementary Metal-Oxide-Semiconductor) 기술을 사용하여 구현할 수 있습니다. 이 두 기술은 디지털 논리 회로에서 널리 사용되며, 각각 고유한 장점을 제공합니다.

2-3-1) TTL 기술을 사용한 NOR 게이트

TTL 기술에서 NOR 게이트는 여러 트랜지스터를 사용하여 구성됩니다.

TTL NOR 게이트는 높은 속도와 신뢰성을 제공하지만, 상대적으로 높은 전력 소비를 특징으로 합니다.

TTL NOR 게이트는 입력 신호 A와 B가 모두 낮은 상태(0)일 때만 출력이 높아집니다.

2-3-2) CMOS 기술을 사용한 NOR 게이트

CMOS 기술에서 NOR 게이트는 p채널과 n채널 MOSFET의 조합으로 구성됩니다.

CMOS NOR 게이트는 낮은 전력 소비와 높은 속도를 제공하며, 현대의 집적 회로에서 널리 사용됩니다.

여기서, 두 개의 PMOS는 병렬로 연결되어 있고, 두 개의 NMOS는 직렬로 연결되어 있습니다.

입력이 모두 0일 때만, PMOS는 켜지고 NMOS는 꺼져서 출력이 높아집니다.

이와 같이, NOR 게이트 회로는 다양한 방식으로 구현될 수 있으며, 각각의 방식은 고유한 특성과 장점을 가지고 있습니다.

회로 설계 시, 사용되는 기술과 구성 요소에 따라 NOR 게이트의 성능과 전력 소비 특성이 달라질 수 있습니다.

이를 통해 NOR 게이트의 동작 원리와 회로 구성을 이해하고, 적절한 상황에 맞는 NOR 게이트 설계를 선택할 수 있습니다.

3. NOR 게이트 회로의 특성 및 성능

3-1) 입력 및 출력 특성

NOR 게이트 회로는 여러 입력을 받을 수 있으며, 모든 입력이 0일 때 출력이 1이 되고, 하나라도 1이면 출력이 0이 됩니다.

여기서 입력이 0인 상태는 논리적 LOW (일반적으로 0V)이며, 입력이 1인 상태는 논리적 HIGH (일반적으로 5V 또는 3.3V)입니다.

NOR 게이트는 이러한 입력 신호를 처리하여, 특정 논리 상태에 따라 출력을 결정합니다.

- 입력 특성 : NOR 게이트의 입력은 일반적으로 디지털 신호로 정의됩니다.

TTL(NOR 게이트의 출력이 1일 때)에서는 입력 전압이 2.0V 이상일 때 HIGH로 간주하고, 0.8V 이하일 때 LOW로 간주합니다.

CMOS 기술에서는 일반적으로 입력 전압이 전원 전압(Vcc)의 절반 이상일 때 HIGH로, 절반 이하일 때 LOW로 간주됩니다. - 출력 특성 : NOR 게이트의 출력은 입력 상태에 따라 결정됩니다.

출력은 전형적으로 전원 전압(Vcc) 또는 접지(GND) 수준의 디지털 신호로 나타납니다.

이 출력을 통해 다음 단계의 디지털 회로로 신호를 전달하거나, 특정 동작을 수행할 수 있습니다.

3-2) 게이트의 응답 시간

NOR 게이트 회로의 응답 시간은 입력 상태가 변한 후 출력 상태가 변할 때까지 걸리는 시간입니다.

이는 중요한 성능 지표로, 회로의 속도를 결정합니다.

- 전파 지연(propagation delay) : 이는 입력 신호의 변화가 게이트를 통해 전파되어 출력에 영향을 미치는 시간입니다.

전파 지연은 상승 시간(rise time)과 하강 시간(fall time)으로 나눌 수 있으며, 각각 입력 신호가 LOW에서 HIGH로, 또는 HIGH에서 LOW로 변할 때 걸리는 시간입니다. - 예를 들어, CMOS NOR 게이트의 경우, 전파 지연은 일반적으로 수 나노초(ns)에서 수십 나노초 범위에 있습니다. TTL 기술에서는 이 시간이 더 짧을 수 있으며, 특히 고속 TTL 게이트는 몇 ns 이내의 전파 지연을 가집니다.

- 반응 속도: NOR 게이트의 반응 속도는 신호 처리 속도와 관련이 있습니다. 빠른 응답 시간을 가진 NOR 게이트는 고속 신호 처리에 적합하며, 주로 고속 통신 또는 처리 시스템에서 사용됩니다.

3-3) 전력 소비 특성

NOR 게이트 회로의 전력 소비 특성은 사용되는 기술과 회로 설계에 따라 크게 다릅니다.

전력 소비는 게이트가 동작 중에 사용하는 전력의 양을 나타내며, 효율적인 회로 설계를 위해 중요한 요소입니다.

- 스태틱 전력 소비(static power consumption) : 이는 회로가 고정된 상태에 있을 때 소비되는 전력입니다.

예를 들어, CMOS NOR 게이트는 스태틱 전력 소비가 매우 낮으며, 입력 신호가 변하지 않는 한 거의 전력을 소비하지 않습니다.

이는 CMOS 기술의 주요 장점 중 하나입니다. - 다이내믹 전력 소비(dynamic power consumption) : 이는 게이트가 전환될 때 소비되는 전력입니다.

입력 신호가 변하고 출력 상태가 변경될 때, 게이트는 전력을 소비합니다.

TTL 기술의 NOR 게이트는 전환 시 비교적 높은 전력을 소비하는 반면, CMOS NOR 게이트는 더 낮은 전력을 소비합니다.

예를 들어, TTL NOR 게이트는 고속 동작을 위해 더 많은 전력을 소비하는 반면, CMOS NOR 게이트는 상대적으로 낮은 전력을 소비하여 효율적입니다.

이는 배터리 구동 장치 또는 에너지 효율이 중요한 시스템에서 CMOS NOR 게이트를 선호하게 만듭니다.

4. NOR 게이트 회로의 장점과 한계

4-1) NOR 게이트의 주요 장점

NOR 게이트 회로는 디지털 시스템에서 다음과 같은 여러 가지 중요한 장점을 제공합니다.

- 기본 빌딩 블록 : NOR 게이트는 모든 논리 연산을 구현할 수 있는 유니버설 게이트입니다.

이는 복잡한 논리 회로를 설계할 때 기본적인 빌딩 블록으로 사용될 수 있음을 의미합니다.

예를 들어, AND, OR, NOT 게이트는 모두 NOR 게이트를 조합하여 구현할 수 있습니다.

예를 들어, 두 개의 NOR 게이트를 직렬로 연결하면 NOT 게이트를 구현할 수 있습니다.

이는 첫 번째 NOR 게이트가 입력을 반전시키고, 두 번째 NOR 게이트가 다시 반전시키는 원리를 이용한 것입니다. - 단순한 설계 : NOR 게이트는 단순하고 이해하기 쉬운 구조를 가지고 있어, 디지털 회로 설계에서 널리 사용됩니다.

단일 NOR 게이트는 두 개 이상의 입력을 처리할 수 있으며, 이는 다양한 입력 조건에서 간단하게 사용할 수 있는 장점을 제공합니다. - 비용 효율적 : NOR 게이트는 비교적 저렴하게 생산할 수 있으며, 특히 CMOS 기술을 사용한 NOR 게이트는 전력 소비가 적어 비용 효율적인 솔루션을 제공합니다.

이는 대규모 통합 회로(VLSI) 설계에서 중요한 요소입니다.

4-2) NOR 게이트의 한계와 단점

NOR 게이트 회로는 장점 외에도 몇 가지 한계와 단점을 가지고 있습니다.

- 속도 제한 : NOR 게이트는 특히 다중 단계를 거친 경우, 응답 시간이 다른 고속 논리 게이트에 비해 느릴 수 있습니다.

이는 고속 처리가 필요한 응용 분야에서는 단점이 될 수 있습니다.

특히, TTL 기술을 사용한 NOR 게이트는 전파 지연 시간이 상대적으로 길어 고속 응용에는 적합하지 않을 수 있습니다.

예를 들어, 고속 통신 시스템에서는 빠른 응답 시간이 필요하며, NOR 게이트의 응답 시간이 느릴 경우, 전체 시스템의 성능에 영향을 미칠 수 있습니다. - 전력 소비 : 비록 CMOS NOR 게이트가 전력 소비 측면에서 효율적이지만, TTL 기술을 사용한 NOR 게이트는 동작 시 상대적으로 많은 전력을 소비할 수 있습니다.

이는 배터리로 구동되는 장치나 에너지 효율이 중요한 시스템에서는 단점이 될 수 있습니다. - 구현의 복잡성 : 다수의 입력을 처리하는 NOR 게이트 회로를 구현하는 것은 비교적 간단하지만, 매우 복잡한 논리 함수를 구현할 때는 여러 개의 NOR 게이트를 조합해야 하므로 회로가 복잡해질 수 있습니다.

Thanks for sharing excellent informations. Your web site is very cool. I’m impressed by the details that you’ve on this site. It reveals how nicely you understand this subject. Bookmarked this website page, will come back for more articles. You, my friend, ROCK! I found simply the info I already searched everywhere and simply could not come across. What an ideal web site.

Thank you so much for your incredibly kind words! I’m truly glad you found the information helpful. Your support and encouragement mean the world to me.

Please let me know if you’re looking for a author for your weblog. You have some really good posts and I think I would be a good asset. If you ever want to take some of the load off, I’d absolutely love to write some material for your blog in exchange for a link back to mine. Please blast me an email if interested. Many thanks!

I’m honored you enjoy the content! At the moment, I’m not actively looking for contributors, but I’ll keep your message in mind in case opportunities open up.

Enjoyed looking through this, very good stuff, regards.

Thank you so much!

I’m really glad you enjoyed it and found the content valuable.

Hello.This article was extremely motivating, particularly since I was browsing for thoughts on this matter last couple of days.

I’m really glad to hear that the article resonated with you!

I enjoy your writing style genuinely loving this site.

Thank you so much for your kind words!

You made a number of nice points there. I did a search on the topic and found nearly all persons will agree with your blog.

Thank you!

It’s encouraging to hear that the points I raised resonate with others as well.

The following time I learn a blog, I hope that it doesnt disappoint me as a lot as this one. I imply, I do know it was my option to read, however I truly thought youd have one thing fascinating to say. All I hear is a bunch of whining about something that you could fix for those who werent too busy searching for attention.

Thank you for your feedback—I’ll keep it in mind.

I like the helpful information you supply to your articles. I will bookmark your weblog and test again here regularly. I’m quite certain I will be told many new stuff right right here! Good luck for the following!

Thank you for your kind words. I’m glad the articles are helpful

Excellent site you have here but I was curious about if you knew of any community forums that cover the same topics talked about in this article? I’d really like to be a part of group where I can get responses from other knowledgeable people that share the same interest. If you have any recommendations, please let me know. Kudos!

I appreciate your interest! I don’t have particular forum recommendations, but I’m glad you found the article helpful.