Contents

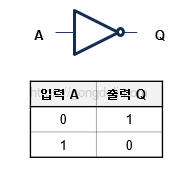

1. NOT 게이트란 무엇인가?

NOT 게이트 논리 회로는 입력 신호를 반전시키는 역할을 합니다.

다른 논리 게이트와 달리 단일 입력만을 가지며, 이 입력 값이 ‘1’(HIGH)이면 출력은 ‘0’(LOW)로, 입력 값이 ‘0’(LOW)이면 출력은 ‘1’(HIGH)로 변환합니다.

이 동작을 “반전” 또는 “부정”이라고 하며, 그래서 NOT 게이트를 인버터(Inverter)라고도 부릅니다.

예를 들어, 입력이 1이라면 출력은 0이 되고, 입력이 0이라면 출력은 1이 됩니다.

진리표를 통해 이 동작을 쉽게 이해할 수 있습니다.

이 진리표에서 볼 수 있듯이, NOT 게이트는 입력 값의 상태를 반대로 바꿉니다.

NOT 게이트 논리 회로는 입력 신호를 반전시키기 위해 전자 회로를 활용합니다.

가장 기본적인 NOT 게이트 회로는 트랜지스터를 사용하여 구현할 수 있으며, 이 회로는 간단하면서도 효과적인 반전 동작을 제공합니다.

이러한 NOT 게이트 논리 회로는 다양한 디지털 시스템에서 신호를 반전시키기 위해 사용되며, 다른 논리 게이트들과 조합하여 더 복잡한 논리 회로를 구축하는 데 중요한 역할을 합니다.

- 연관 참조 : 디지털 논리 게이트, 입.출력, 논리 상태와 전압 레벨

- 연관 참조 : AND 게이트 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : OR 게이트 논리 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : NAND 게이트 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : NOR 게이트 회로, 회로 구성, 특성 및 성능, 장점 3개와 한계

- 연관 참조 : XOR 게이트 회로 설계, 회로 구성, 특성 및 성능, 장점 3개와 한계

- 연관 참조 : XNOR 게이트 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : Buffer 회로 설계, 회로 설계의 기본 구성, 설계 고려 사항

2. NOT 게이트 논리 회로 구성

NOT 게이트 논리 회로는 디지털 시스템에서 입력 신호를 반전시키는 데 사용되는 기본적인 구성 요소입니다.

이 회로는 다양한 기술과 구성 요소를 사용하여 구현할 수 있으며, 각 방식은 고유의 장점과 특성을 가지고 있습니다.

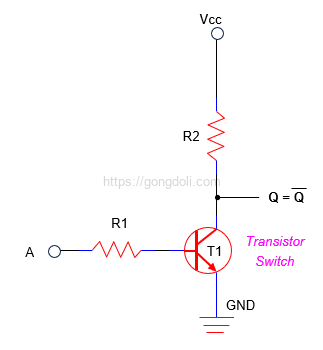

2-1) 트랜지스터를 사용한 NOT 게이트

트랜지스터 기반의 NOT 게이트 논리 회로는 가장 기본적이고 널리 사용되는 구성 중 하나입니다.

트랜지스터는 스위치처럼 동작하여 입력 신호의 상태에 따라 회로를 개폐하고, 이를 통해 출력 신호를 반전시킵니다

NPN 트랜지스터를 사용한 NOT 게이트의 동작 원리를 설명하면 다음과 같습니다.

입력 신호가 LOW (0)이면, 트랜지스터는 차단 상태에 있습니다.

따라서 출력은 전원(Vcc)에 의해 HIGH (1) 상태가 됩니다.

입력 신호가 HIGH (1)이면, 트랜지스터는 도통 상태가 되어 전류가 흐르고, 출력은 GND(0V)로 연결되어 LOW (0) 상태가 됩니다.

다시 설명하면, 입력이 LOW일 때, 트랜지스터의 베이스-에미터 전압이 낮아져 트랜지스터가 차단되고, 출력은 HIGH가 됩니다.

입력이 HIGH일 때, 트랜지스터의 베이스-에미터 전압이 높아져 트랜지스터가 도통되어 출력이 LOW가 됩니다.

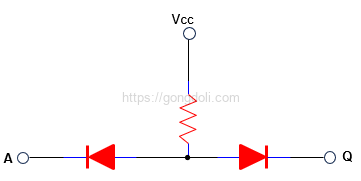

2-2) 다이오드를 사용한 NOT 게이트

다이오드를 사용하여 NOT 게이트 논리 회로를 구성하는 방법은 일반적이지 않지만, 이해를 돕기 위해 간단한 설명을 제공합니다.

다이오드는 입력 신호가 특정 방향으로만 흐르도록 하는 특성을 이용할 수 있습니다.

그러나 실제로 다이오드만으로 NOT 게이트를 만드는 것은 복잡하고 비효율적이기 때문에, 일반적으로는 다이오드를 다른 구성 요소와 함께 사용합니다.

2-3) TTL 및 CMOS 기술을 사용한 NOT 게이트

TTL(Transistor-Transistor Logic) 및 CMOS(Complementary Metal-Oxide-Semiconductor) 기술은 현대 디지털 회로에서 가장 널리 사용되는 두 가지 기술입니다.

이 기술들은 고속 동작과 낮은 전력 소비를 제공하며, NOT 게이트를 포함한 다양한 논리 게이트를 구현하는 데 사용됩니다.

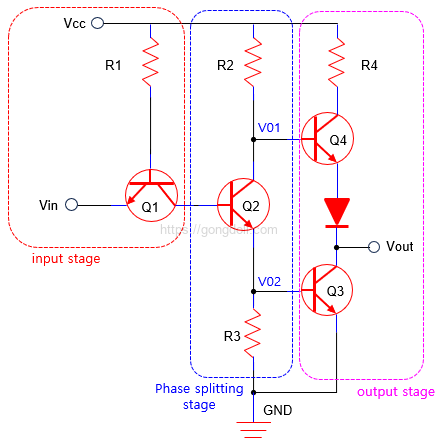

2-3-1) TTL 기반의 NOT 게이트

① Input Stage

입력 단계의 트랜지스터 Q1은 전류 제어(스티어링) 역할을 합니다.

이 트랜지스터는 전류를 제어하는 방식으로, 마치 두 개의 다이오드를 맞대어 연결한 것처럼 동작합니다. Q1은 순방향 모드 또는 역방향 모드로 작동하며, 이 과정에서 두 번째 단계의 트랜지스터 Q2의 베이스로 전류를 보내거나, 반대로 전류를 빼앗아 방전시킵니다.

트랜지스터의 순방향 전류 이득(βF)은 역방향 전류 이득(βR)보다 훨씬 큽니다.

이를 통해 Q1은 더 많은 전류를 제공할 수 있으며, 이는 Q2의 베이스가 빠르게 방전되도록 도와줍니다.

결과적으로, Q2가 꺼질 때 더 빠르게 베이스 전류를 방출하게 되어 Q2의 반응 시간이 향상됩니다.

② Phase Splitting Stage

두 번째 단계 트랜지스터인 Q2는 풀업(pull-up)과 풀다운(pull-down) 출력 단계를 모두 구동하기 위한 위상 분할(phase splitter) 트랜지스터입니다.

이 트랜지스터는 입력 상태를 반대 위상으로 만들어 출력 트랜지스터를 상반되는 위상으로 구동할 수 있도록 합니다.

즉, 출력 트랜지스터들이 교대로 동작할 수 있게 해주는 역할을 합니다.

Q2 베이스 = Low 이면, V01= High, V02 = Low

Q2 베이스 = High 이면, V01= Low, V02 = High

예를 들어, 그림 3에서 볼 수 있듯이, Q3가 켜져 있을 때 Q4는 꺼져 있고, Q4가 켜져 있을 때 Q3는 꺼져 있게 됩니다.

이를 통해 Q3와 Q4가 반대 위상으로 동작하게 만들어, 회로의 효과적인 스위칭을 가능하게 합니다.

③ Output Stage

그림 4에서 보듯이, 출력 트랜지스터 쌍인 Q3와 Q4, 그리고 다이오드 D1은 토템폴(totem-pole) 출력 구성으로 불립니다.

이 출력 구성은 전류를 능동적으로 소싱(sourcing)하거나 싱킹(sinking)할 수 있는 능력을 제공하며, 이는 특히 용량성 부하(capacitive load)를 구동하는 데 유용합니다.

또한, R4 저항은 VCC로부터의 전류를 제한하는 역할을 합니다. 안정된 상태에서는 한 번에 하나의 트랜지스터만 켜져 있게 됩니다.

그림 4 출력 단계

다이오드 D1은 Q4의 유효 턴온 전압을 높이는 역할을 하며, 이를 통해 Q3가 완전히 켜지기 전에 Q4를 꺼지게 할 수 있습니다.

이것은 논리 상태 전환 중에 출력 단계에서 발생할 수 있는 큰 서지 전류(surge current)를 방지하는 데 도움이 됩니다.

또한, R4 저항은 출력 단계에서 흐를 수 있는 전류를 제한하는 역할도 합니다.

그러나 이 구성의 단점은, 그림에서 볼 수 있듯이 논리적 높은 전압(Logic High Voltage)이 다이오드의 전압 강하만큼 감소된다는 점입니다.

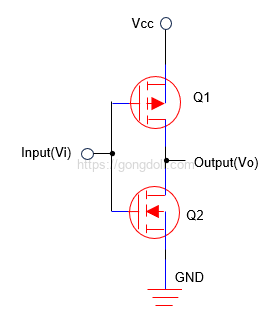

2-3-2) CMOS 기반의 NOT 게이트

하나의 n채널 MOSFET(NMOS)과 하나의 p채널 MOSFET(PMOS)으로 구성된 CMOS NOT 게이트 논리 회로를 보여줍니다.

입력은 두 트랜지스터의 게이트 단자에 연결되고, 출력은 두 드레인 단자에 연결됩니다.

입력(Vi)에 +V(논리 1)를 인가하면, 트랜지스터 Q2는 “켜짐(on)” 상태가 되고, 트랜지스터 Q1은 “꺼짐(off)” 상태로 유지됩니다.

이 조건에서는 출력 전압(Vo)이 거의 0V(논리 0)로 나타납니다.

반면에 입력을 접지(Vi = 0V)에 연결하면, 트랜지스터 Q2는 “꺼짐(off)” 상태가 되고, 트랜지스터 Q1은 “켜짐(on)” 상태가 됩니다.

이때 출력 전압은 거의 +V(논리 1)에 가깝게 됩니다.

다시 정리하면, 트랜지스터 기반의 NOT 게이트는 NPN 트랜지스터를 사용하여 입력 신호를 반전시킵니다.

다이오드를 사용한 NOT 게이트는 덜 일반적이지만, 다이오드와 저항을 사용하여 기본적인 반전 동작을 구현할 수 있습니다.

TTL과 CMOS 기술은 각각 트랜지스터 및 PMOS/NMOS 트랜지스터를 사용하여 효율적인 NOT 게이트를 구현할 수 있습니다.

3. NOT 게이트의 특성 및 성능

NOT 게이트는 입력 신호를 반전시켜 출력하는 간단하면서도 중요한 논리 회로입니다.

3-1) 입력 및 출력 특성

NOT 게이트 논리 회로의 가장 기본적인 특성은 입력과 출력의 관계입니다.

NOT 게이트는 단일 입력을 받고, 이를 반전시켜 출력합니다.

즉, 입력이 논리 1이면 출력은 논리 0이고, 입력이 논리 0이면 출력은 논리 1이 됩니다.

실제로, CMOS 기술을 사용한 NOT 게이트 논리 회로에서는 p채널과 n채널 MOSFET이 함께 사용됩니다.

입력이 1일 때, n채널 MOSFET이 켜지고(p채널은 꺼짐), 출력은 낮은 전압 상태(0)가 됩니다.

반대로, 입력이 0일 때는 p채널 MOSFET이 켜지고(n채널은 꺼짐), 출력은 높은 전압 상태(1)가 됩니다.

3-2) 게이트의 응답 시간

NOT 게이트 논리 회로의 응답 시간은 입력 신호가 변경된 후 출력 신호가 그에 맞춰 변경되기까지 걸리는 시간입니다.

이는 게이트가 얼마나 빠르게 상태를 반전시킬 수 있는지를 나타냅니다.

응답 시간은 여러 요인에 의해 영향을 받을 수 있습니다.

- 회로의 용량(Capacitance) : 높은 용량은 전하의 축적과 방출에 더 많은 시간이 필요하게 하여 응답 시간을 증가시킵니다.

- 트랜지스터의 속도(Switching Speed) : 트랜지스터의 물리적 특성과 기술적 한계는 전환 속도에 영향을 미칩니다.

- 전원 전압(Power Supply Voltage) : 더 높은 전압은 더 빠른 응답을 가능하게 하지만, 전력 소비도 증가시킬 수 있습니다.

CMOS 기술을 사용한 NOT 게이트는 일반적으로 높은 속도를 제공하며, 응답 시간은 보통 나노초(ns) 단위로 측정됩니다.

3-3) 전력 소비 특성

NOT 게이트 논리 회로의 전력 소비는 회로의 효율성과 관련이 깊습니다.

특히, 디지털 회로가 점점 더 복잡해지면서 전력 효율은 매우 중요한 요소가 되었습니다.

NOT 게이트의 전력 소비는 두 가지 주요 요소에 의해 결정됩니다.

- 정적 전력 소비(Static Power Consumption) : 입력 상태에 관계없이 회로가 전력을 소비하는 정도입니다.

CMOS NOT 게이트는 매우 낮은 정적 전력 소비를 가지고 있으며, 주로 트랜지스터가 “껐을 때” 거의 전류를 소비하지 않기 때문에 정지 상태에서는 매우 적은 전력을 소모합니다. - 동적 전력 소비(Dynamic Power Consumption) : 입력이 변할 때, 즉 게이트가 스위칭할 때 소비되는 전력입니다.

이 전력은 용량성 부하의 충전 및 방전으로 인해 발생하며, 스위칭 주파수와 전원 전압의 제곱에 비례합니다.

고주파에서 작동할수록 더 많은 동적 전력을 소비하게 됩니다.

이와 같이, NOT 게이트 논리 회로는 고속 동작과 낮은 전력 소비를 결합하여 매우 효율적인 반전 기능을 제공합니다.

4. NOT 게이트의 장점과 한계

4-1) NOT 게이트의 주요 장점

NOT 게이트 논리 회로는 그 단순함에도 불구하고 여러 가지 중요한 장점을 가지고 있습니다.

- 간단한 설계와 구현

NOT 게이트는 단일 입력과 단일 출력을 가지는 가장 간단한 논리 게이트입니다.

이로 인해 설계와 구현이 매우 간단하며, 다양한 전자 회로와 시스템에 쉽게 통합될 수 있습니다.

특히, CMOS 기술을 사용하는 NOT 게이트는 소수의 트랜지스터만으로 구성되기 때문에 매우 경제적입니다. - 빠른 응답 시간

NOT 게이트는 매우 빠른 응답 시간을 자랑합니다.

이는 입력 신호가 변경될 때 출력이 거의 즉시 반전된다는 것을 의미합니다.

이러한 특성은 고속의 디지털 회로에서 매우 중요한 요소로 작용합니다. - 낮은 전력 소비

특히 CMOS 기반의 NOT 게이트 논리 회로는 매우 낮은 정적 전력 소비를 자랑합니다.

이는 회로가 대기 상태일 때 거의 전력을 소비하지 않으며, 스위칭 동작 동안에도 비교적 적은 전력을 사용합니다.

따라서 배터리로 구동되는 장치나 에너지 효율이 중요한 시스템에 매우 적합합니다. - 광범위한 응용

NOT 게이트는 단일 기능으로 끝나지 않고, 더 복잡한 논리 회로를 구성하는 기본 요소로 사용됩니다.

예를 들어, 다양한 논리 게이트 및 조합 논리 회로에서 NOT 게이트는 필수적인 역할을 합니다.

4-2) NOT 게이트의 한계와 단점

NOT 게이트 논리 회로는 여러 가지 장점을 가지고 있지만, 몇 가지 한계와 단점도 존재합니다.

- 단일 기능

NOT 게이트는 입력 신호를 단순히 반전하는 기능만을 제공합니다.

이는 논리적으로 다른 기능을 수행하기 위해서는 다른 논리 게이트와 결합해야 한다는 것을 의미합니다.

단독으로 사용할 수 있는 논리 연산이 매우 제한적입니다. - 스위칭 전류 문제

CMOS NOT 게이트에서, 스위칭 과정 동안 잠시 동안 두 트랜지스터가 모두 켜질 수 있습니다.

이 상태에서 전류가 갑자기 증가하여 과도 전류가 흐를 수 있으며, 이는 회로의 열적 스트레스를 증가시키고 전력 소모를 일시적으로 높일 수 있습니다. - 출력 드라이브 능력 제한

NOT 게이트는 출력에서 제공할 수 있는 전류가 제한적입니다.

특히, 많은 부하를 구동해야 하는 경우에는 출력 전류가 충분하지 않을 수 있습니다.

이를 극복하기 위해 추가적인 버퍼링 또는 드라이버 회로가 필요할 수 있습니다. - 전압 변동에 민감

NOT 게이트는 전원 전압의 변동에 민감하게 반응할 수 있습니다.

특히 CMOS NOT 게이트는 전원 전압이 안정적이지 않으면, 스위칭 특성이나 출력 레벨이 변할 수 있습니다.

Having read this I thought it was very informative. I appreciate you taking the time and effort to put this article together. I once again find myself spending way to much time both reading and commenting. But so what, it was still worth it!

Thank you so much for your kind words! I’m glad you found it informative, and I truly appreciate your time and thoughtful comments.

I’m not sure why but this blog is loading extremely slow for me. Is anyone else having this issue or is it a issue on my end? I’ll check back later and see if the problem still exists.

Thanks for letting me know! I’m sorry to hear you’re experiencing slow loading times. I haven’t received similar reports yet, but I’ll look into it and see if anything’s going on.

Nice post. I study one thing more difficult on totally different blogs everyday. It’s going to at all times be stimulating to read content from other writers and observe a bit one thing from their store. I’d want to make use of some with the content material on my blog whether you don’t mind. Natually I’ll give you a link on your internet blog. Thanks for sharing.

Thank you so much for your thoughtful comment!

I’d be happy for you to use part of the content on your blog — as long as you kindly include a link back to the original source.

I truly appreciate your interest and support!

It’s actually a great and helpful piece of information. I’m happy that you shared this helpful info with us. Please keep us informed like this. Thanks for sharing.

Thank you so much for your kind words!

I’m really glad the information was helpful.

Generally I don’t read post on blogs, but I wish to say that this write-up very forced me to try and do so! Your writing style has been amazed me. Thanks, very nice article.

Thank you so much for your kind words!

I’m truly honored that the post caught your attention and encouraged you to read.

I’ll keep doing my best to share more content that resonates!

Hey There. I found your blog using msn. This is a very well written article. I will make sure to bookmark it and return to read more of your useful information. Thanks for the post. I will definitely return.

Thanks a lot—looking forward to having you back!

I haven?¦t checked in here for some time as I thought it was getting boring, but the last several posts are good quality so I guess I will add you back to my daily bloglist. You deserve it my friend 🙂

Thank you—I’m glad you enjoyed the recent posts.

of course like your web-site however you need to check the spelling on quite a few of your posts. Several of them are rife with spelling issues and I in finding it very bothersome to tell the truth on the other hand I will surely come again again.

Thank you for pointing that out. I’ll be more careful with spelling in future posts.

Real clean website , appreciate it for this post.

Thank you! I’m glad you liked the post and found the site clean and enjoyable.

Aw, this was a very nice post. In idea I wish to put in writing like this moreover – taking time and precise effort to make a very good article… however what can I say… I procrastinate alot and in no way seem to get one thing done.

Thank you for your kind words. I’m glad you enjoyed the post.

Outstanding post, I think blog owners should larn a lot from this website its very user pleasant.

Thank you so much! I’m delighted you find the site user‑friendly, and I truly appreciate your kind words of encouragement.