Contents

1. OR 게이트 논리 회로란 무엇인가?

디지털 회로에서 OR 게이트 논리 회로는 매우 중요한 역할을 합니다.

이 게이트는 여러 입력 중 하나라도 ‘1’일 때, 출력이 ‘1’이 되는 논리 연산을 수행합니다.

1-1) OR 게이트의 정의

OR 게이트는 논리 연산에서 “또는”이라는 개념을 적용하는 디지털 논리 회로입니다.

이 게이트의 주요 기능은 입력된 여러 신호 중 하나 이상이 ‘참(True)’일 경우, 출력이 ‘참(True)’이 되는 것입니다.

OR 게이트는 전자공학에서 자주 사용되며, 다양한 디지털 시스템과 회로에서 핵심 요소로 활용됩니다.

OR 게이트의 기호는 아래와 같이 생겼습니다.

여기서, A와 B는 입력이고 Q는 출력입니다.

OR 게이트는 두 개 이상의 입력을 받을 수 있지만, 가장 기본적인 형태는 두 개의 입력을 갖는 것입니다.

이 경우, 출력 Q는 입력 A와 B 중 하나라도 ‘1’일 때 ‘1’이 됩니다.

1-2) OR 게이트의 기본 원리

OR 게이트 논리 회로의 동작 원리는 매우 직관적입니다.

OR 게이트는 입력 값 중 하나라도 ‘1’인 경우에만 출력을 ‘1’로 설정합니다.

이를 이해하기 쉽게 설명하기 위해, OR 게이트의 진리표를 살펴보겠습니다.

이 진리표를 통해 OR 게이트의 동작을 쉽게 이해할 수 있습니다.

입력 A와 B 중 하나라도 ‘1’이면, 출력 Q는 ‘1’입니다.

단, 두 입력이 모두 ‘0’인 경우에만 출력이 ‘0’이 됩니다.

이러한 논리는 다음과 같은 실제 상황에서 응용될 수 있습니다.

예를 들어, 두 개의 스위치(A와 B)가 전등을 켤 수 있는 회로가 있다고 생각해 보겠습니다.

스위치 중 하나라도 켜져 있으면(1), 전등은 켜집니다(1).

이것이 OR 게이트의 기본 원리와 동일합니다.

또 다른 예로, 데이터 전송 과정에서 오류를 감지하기 위해 여러 신호를 모니터링하는 시스템이 있습니다.

이 시스템은 어느 한 신호라도 오류를 나타내면(1), 전체 시스템이 오류 상태로 간주(1)하고 대처할 수 있습니다.

이 역시 OR 게이트의 원리를 사용한 예입니다.

OR 게이트 논리 회로는 이러한 기본 원리에 따라 구성되며, 다양한 전자 시스템에서 신호 처리 및 결정 로직의 중요한 요소로 사용됩니다.

OR 게이트는 여러 입력 조건을 검사하고, 하나라도 참이면 출력을 참으로 설정하는 단순하지만 강력한 디지털 논리 요소입니다.

- 연관 참조 : 디지털 논리 게이트, 입.출력, 논리 상태와 전압 레벨

- 연관 참조 : AND 게이트 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : NOT 게이트 논리 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : NAND 게이트 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : NOR 게이트 회로, 회로 구성, 특성 및 성능, 장점 3개와 한계

- 연관 참조 : XOR 게이트 회로 설계, 회로 구성, 특성 및 성능, 장점 3개와 한계

- 연관 참조 : XNOR 게이트 회로, 회로 구성, 특성과 성능, 장점 4개와 한계

- 연관 참조 : Buffer 회로 설계, 회로 설계의 기본 구성, 설계 고려 사항

2. OR 게이트의 회로 구성

OR 게이트 논리 회로는 입력 중 하나라도 참(True)일 때 출력을 참으로 만드는 기능을 수행합니다.

이러한 논리를 구현하는 방법에는 여러 가지가 있으며, 트랜지스터, 다이오드, TTL 및 CMOS 기술을 사용한 방법이 대표적입니다.

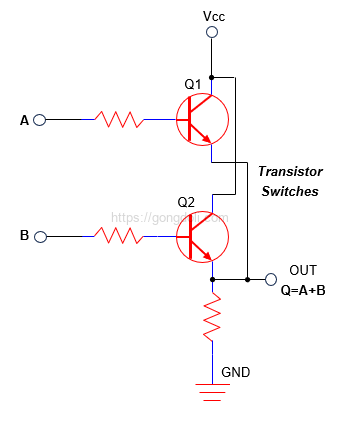

2-1) 트랜지스터를 사용한 OR 게이트

트랜지스터는 현대 디지털 회로에서 가장 많이 사용되는 구성 요소 중 하나입니다.

OR 게이트 논리 회로를 구현하는 데도 트랜지스터를 사용할 수 있습니다.

트랜지스터를 사용한 기본적인 OR 게이트 회로는 다음과 같습니다.

위 그림에서 보듯이, OR 게이트는 두 개의 NPN 트랜지스터가 병렬로 연결되어 있습니다.

여기서 각 트랜지스터의 컬렉터는 공통 출력(Q)과 연결되어 있고, 에미터는 그라운드(GND)에 연결되어 있습니다.

베이스에는 각각 입력(A와 B)이 연결됩니다.

이 회로의 동작 원리는 다음과 같습니다.

입력 A 또는 B 중 하나가 ‘1’ (높은 전압, 예: +5V)이면 해당 트랜지스터는 포화 상태가 됩니다.

이로 인해 트랜지스터는 컬렉터와 에미터 간의 전류가 흐르게 되어, 출력(Y)이 ‘1’로 설정됩니다.

만약 입력 A와 B가 모두 ‘0’ (낮은 전압, 예: 0V)이면, 두 트랜지스터는 모두 차단 상태가 되고, 컬렉터-에미터 간의 전류가 흐르지 않아 출력(Y)는 ‘0’으로 유지됩니다.

이와 같은 트랜지스터 기반의 OR 게이트 논리 회로는 빠른 응답 시간과 비교적 적은 전력 소모로 인해 다양한 디지털 회로에서 사용됩니다.

2-2) 다이오드를 사용한 OR 게이트

다이오드를 사용하여 OR 게이트 논리 회로를 구현하는 것은 가장 간단하고 직관적인 방법 중 하나입니다.

다이오드는 전류가 한 방향으로만 흐르게 하는 특성을 가지고 있습니다.

이를 이용하여 OR 게이트를 구성할 수 있습니다.

다이오드를 사용한 기본적인 OR 게이트 회로는 다음과 같습니다.

이 회로의 동작 원리는 다음과 같습니다.

각 입력(A와 B)은 각각의 다이오드의 애노드(양극)에 연결되어 있습니다.

다이오드의 캐소드(음극)는 공통 출력(Q)와 연결됩니다.

다이오드는 전류가 애노드에서 캐소드로 흐를 때만 통과시키므로, 입력 A 또는 B 중 하나가 ‘1’(높은 전압, 예: +5V)일 때, 해당 다이오드를 통해 전류가 흐르고, 출력(Q)는 ‘1’이 됩니다.

만약 입력 A와 B가 모두 ‘0’(낮은 전압, 예: 0V)이면, 두 다이오드 모두 전류를 통과시키지 않으므로 출력(Q)는 ‘0’이 됩니다.

이 다이오드 기반 OR 게이트는 단순하고, 소형화가 용이하며, 저전력 소모를 자랑하지만, 전압 강하가 발생할 수 있어 다른 복잡한 회로에는 잘 사용되지 않습니다.

2-3) TTL 및 CMOS 기술을 사용한 OR 게이트

TTL (Transistor-Transistor Logic)과 CMOS (Complementary Metal-Oxide-Semiconductor)는 디지털 회로에서 가장 널리 사용되는 두 가지 기술입니다.

이들은 각각 고유한 특성과 장점을 가지고 있으며, OR 게이트 논리 회로를 구현하는 데 자주 사용됩니다.

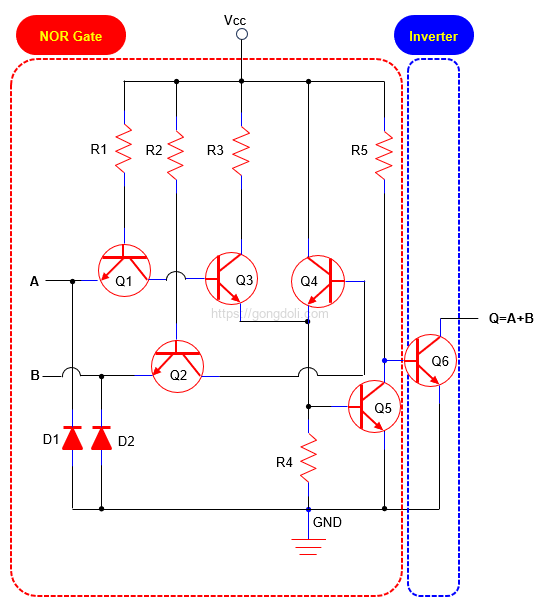

2-3-1) TTL OR 게이트

TTL OR 게이트는 주로 트랜지스터로 구성되며, 빠른 스위칭 속도와 높은 신뢰성을 제공합니다.

TTL 기술을 사용한 OR 게이트의 기본 회로는 다음과 같습니다.

이 회로에서 두 개의 트랜지스터의 컬렉터는 공통 출력에 연결되어 있습니다.

입력 A와 B는 각각의 트랜지스터의 베이스에 연결되며, 이들 중 하나가 ‘1’일 때 해당 트랜지스터가 활성화되어 출력을 ‘1’로 설정합니다.

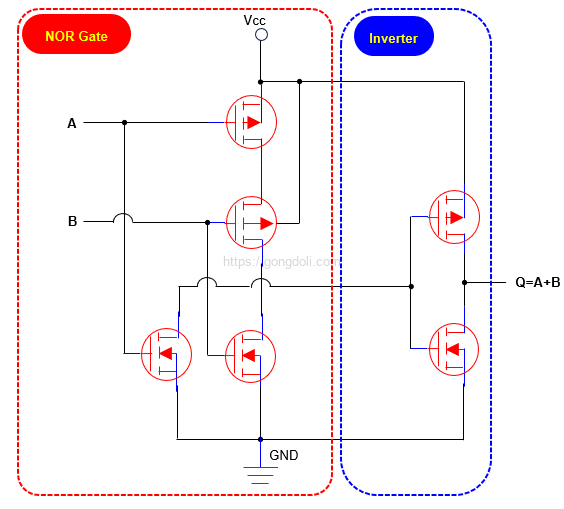

2-3-2) CMOS OR 게이트

CMOS OR 게이트는 N채널과 P채널 MOSFET을 사용하여 구현됩니다.

CMOS 기술은 낮은 전력 소모와 높은 입력 저항을 특징으로 합니다.

CMOS OR 게이트의 기본 회로는 다음과 같습니다.

CMOS OR 게이트는 두 개의 P채널 MOSFET이 상단에, 두 개의 N채널 MOSFET이 하단에 위치하여 구성됩니다.

입력 A와 B 중 하나라도 ‘1’이면, 해당 MOSFET이 활성화되어 출력(Y)는 ‘1’로 설정됩니다.

TTL과 CMOS 기술을 사용한 OR 게이트 회로는 그들의 독특한 특성으로 인해 각기 다른 응용 분야에서 널리 사용됩니다.

이처럼 OR 게이트 논리 회로는 다양한 방법으로 구현될 수 있으며, 각기 다른 기술과 구성 요소에 따라 그 성능과 특성이 달라집니다.

OR 게이트 논리 회로는 디지털 시스템의 기본적인 구성 요소로서, 신호의 논리적 결합을 통해 다양한 기능을 수행합니다.

3. OR 게이트의 특성 및 성능

OR 게이트 논리 회로는 디지털 시스템에서 중요한 역할을 하며, 그 성능과 특성은 시스템의 전반적인 효율성과 작동에 큰 영향을 미칩니다.

3-1) 입력 및 출력 특성

OR 게이트 논리 회로의 입력 및 출력 특성은 게이트가 입력 신호를 어떻게 받아들이고 처리하며, 이를 통해 어떤 출력을 생성하는지 설명합니다.

OR 게이트는 두 개 이상의 입력을 받아들이며, 출력은 다음과 같은 논리적 규칙에 따라 결정됩니다.

(진리표는 위에 참조)

- 입력 특성: OR 게이트는 일반적으로 2개 이상의 입력을 가질 수 있습니다.

각 입력이 ‘1’(HIGH)일 경우 해당 입력은 게이트를 활성화시키며, 전체 출력은 ‘1’이 됩니다.

모든 입력이 ‘0’(LOW)일 경우에만 출력은 ‘0’이 됩니다. - 출력 특성: OR 게이트의 출력은 입력 중 하나라도 ‘1’이면 ‘1’이 됩니다.

즉, OR 게이트의 논리는 “하나라도 참이면 참”이라는 법칙을 따릅니다.

3-2) 게이트의 응답 시간

OR 게이트 논리 회로의 응답 시간은 입력 신호가 변경된 후 출력 신호가 안정된 상태로 전환되는 데 걸리는 시간을 의미합니다.

이는 디지털 회로에서 매우 중요한 성능 지표로 간주됩니다.

- 응답 시간(Tpd) : 게이트의 응답 시간은 일반적으로 전파 지연 시간(Tpd)으로 정의됩니다.

이는 입력 신호가 변할 때 출력 신호가 해당 변화를 반영하기까지 걸리는 시간입니다.

예를 들어, 입력 A나 B가 ‘0’에서 ‘1’로 변할 때, OR 게이트의 출력 Y가 ‘0’에서 ‘1’로 변하기까지 걸리는 시간이 전파 지연 시간입니다. - 기술별 응답 시간 : TTL과 CMOS 같은 다른 기술들은 고유한 응답 시간을 가집니다.

일반적으로, TTL 기술은 빠른 스위칭 속도를 제공하지만, CMOS는 더 낮은 전력 소모와 긴 응답 시간을 제공합니다.

CMOS 기술을 사용한 OR 게이트는 높은 효율성과 낮은 전력 소비로 인해 현대의 저전력 장치에 많이 사용됩니다.

응답 시간은 고속 데이터 처리와 통신을 필요로 하는 시스템에서 특히 중요합니다.

응답 시간이 짧을수록 시스템의 전체 성능이 향상될 수 있습니다.

3-3) 전력 소비 특성

OR 게이트 논리 회로의 전력 소비 특성은 회로가 동작할 때 소비하는 전력의 양을 나타냅니다.

이는 전자 장치의 배터리 수명과 전체적인 에너지 효율성에 직접적인 영향을 미칩니다.

- 정적 전력 소비 : OR 게이트는 정적 상태(즉, 입력이 변하지 않는 상태)에서 전력 소비를 최소화하도록 설계되었습니다.

다이오드 기반 OR 게이트는 전력 소비가 매우 낮으며, 트랜지스터 기반 OR 게이트는 약간 더 많은 전력을 소비할 수 있습니다.

CMOS 기술을 사용한 OR 게이트는 정적 전력 소비가 거의 없으며, 이는 CMOS 회로가 정적 상태에서 전류를 거의 소모하지 않기 때문입니다. - 동적 전력 소비 : 입력 신호가 변할 때 게이트의 내부 회로는 전환 상태에서 전류를 소모하게 되며, 이는 동적 전력 소비로 나타납니다.

TTL 기술을 사용한 OR 게이트는 상대적으로 더 많은 전력을 소모하며, 이는 빠른 응답 시간과 높은 전류 흐름 때문입니다.

CMOS OR 게이트는 동적 전력 소비가 낮으며, 이는 낮은 전압 스윙과 작은 기생 용량 덕분입니다.

전력 소비는 배터리로 구동되는 휴대용 장치나 에너지 효율이 중요한 시스템에서 중요한 요소입니다.

OR 게이트 논리 회로의 설계자는 전력 소비 특성을 최적화하여 시스템의 전체 효율성을 높일 수 있습니다.

OR 게이트 논리 회로는 디지털 시스템에서 매우 중요한 구성 요소로서, 다양한 특성과 성능 지표에 따라 시스템의 효율성과 기능에 영향을 미칩니다.

입력 및 출력 특성, 응답 시간, 전력 소비 특성은 OR 게이트의 설계 및 선택에 중요한 기준이 되며, 이를 통해 최적의 성능을 발휘할 수 있습니다.

4. OR 게이트의 장점과 한계

OR 게이트 논리 회로는 디지털 회로 설계에서 매우 중요한 역할을 합니다. 이 회로는 다양한 시스템에서 여러 조건 중 하나라도 충족되면 원하는 동작을 수행하게 하는 데 필수적입니다.

4-1) OR 게이트의 주요 장점

OR 게이트 논리 회로는 그 간단한 구조와 유용성 덕분에 다양한 응용 분야에서 널리 사용됩니다.

그 주요 장점은 다음과 같습니다.

- 단순한 설계 : OR 게이트는 두 개 이상의 입력 중 하나라도 참이면 출력을 참으로 만드는 단순한 논리를 따릅니다.

이러한 단순함 덕분에 설계와 구현이 비교적 쉽고 직관적입니다.

예를 들어, 보안 시스템에서 여러 센서 중 하나라도 활성화되면 경보를 울리도록 하는 데 OR 게이트를 사용할 수 있습니다.

이 경우, 여러 센서의 출력을 OR 게이트의 입력으로 연결하면 간단하게 시스템을 구성할 수 있습니다. - 광범위한 응용 : OR 게이트는 다양한 디지털 시스템에서 필수적입니다.

특히 다중 조건을 체크해야 하는 경우에 유용합니다.

예를 들어, 산업 자동화 시스템에서 여러 안전 스위치 중 하나라도 활성화되면 장비를 중지시키는 데 사용될 수 있습니다. - 다중 입력 처리 : OR 게이트는 다수의 입력을 처리할 수 있습니다.

이는 복잡한 논리 연산이 필요한 경우에도 효과적으로 사용할 수 있음을 의미합니다.

다중 입력 OR 게이트를 사용하면 복잡한 다중 조건 논리를 단일 게이트로 쉽게 구현할 수 있습니다. - 낮은 전력 소비 : 특히 CMOS 기술을 사용하는 OR 게이트는 매우 낮은 전력 소비를 자랑합니다.

이는 배터리 수명이 중요한 모바일 및 휴대용 장치에서 매우 중요한 특성입니다.

4-2) OR 게이트의 한계와 단점

OR 게이트 논리 회로는 많은 장점을 가지고 있지만, 몇 가지 한계와 단점도 존재합니다.

- 제한된 논리 표현 : OR 게이트는 논리적 합(OR)만 표현할 수 있으며, 복잡한 논리 연산에는 다른 논리 게이트와 함께 사용해야 합니다.

예를 들어, XOR 또는 AND와 같은 논리 연산은 OR 게이트만으로는 구현할 수 없습니다. - 소음 민감도 : OR 게이트는 입력 신호 중 하나라도 ‘1’로 변하면 출력이 ‘1’로 변하기 때문에, 노이즈가 많은 환경에서는 오류를 발생시킬 수 있습니다.

이는 입력 신호의 작은 변동이 출력에 큰 영향을 미칠 수 있음을 의미합니다. - 전력 소모 증가 : OR 게이트는 입력이 증가함에 따라 더 많은 전력을 소모할 수 있습니다.

이는 특히 TTL 기술을 사용한 OR 게이트에서 더 두드러지며, 다중 입력을 사용하는 경우 전력 소모가 증가할 수 있습니다. - 복잡한 회로 설계 시 제한 : OR 게이트만으로는 복잡한 논리 회로를 설계하는 데 한계가 있을 수 있습니다.

복잡한 연산이 필요한 경우에는 여러 종류의 논리 게이트를 결합하여 사용해야 합니다.

It’s hard to find knowledgeable people on this topic, but you sound like you know what you’re talking about! Thanks

Thank you so much for your appreciation!

Wow! Thank you! I always wanted to write on my blog something like that. Can I include a fragment of your post to my website?

I really appreciate your interest—thanks so much!

Yes, you’re welcome to include a short excerpt, as long as you give proper credit and link back to the original post. Happy blogging!

I’ve been exploring for a bit for any high quality articles or blog posts on this sort of area . Exploring in Yahoo I at last stumbled upon this website. Reading this info So i am happy to convey that I have a very good uncanny feeling I discovered just what I needed. I most certainly will make certain to don’t forget this website and give it a glance regularly.

We’re truly honored by your thoughtful message!

It’s wonderful to hear that our content matched exactly what you were looking for.

We’ll continue sharing insightful and high-quality posts, and you’re always welcome to drop by anytime.

Thank you again for your kind support — it means a lot to us!

Today, I went to the beachfront with my children. I found a sea shell and gave it to my 4 year old daughter and said “You can hear the ocean if you put this to your ear.” She placed the shell to her ear and screamed. There was a hermit crab inside and it pinched her ear. She never wants to go back! LoL I know this is totally off topic but I had to tell someone!

Thanks for sharing that story, it definitely made me smile!

Those are yours alright! . We at least need to get these people stealing images to start blogging! They probably just did a image search and grabbed them. They look good though!

Haha, I appreciate the sharp eye! It’s wild how often images get snatched without credit.

If they’re inspired enough to start blogging, maybe something good will come of it! Thanks for noticing — and glad you think they look good!

Great items from you, man. I’ve be aware your stuff previous to and you are just too wonderful. I really like what you have got here, really like what you are stating and the best way wherein you assert it. You make it entertaining and you continue to take care of to stay it wise. I can not wait to learn much more from you. This is actually a terrific site.

Thank you so much for your incredibly kind and encouraging words!

I’m truly grateful that you’ve been following along and enjoying the way things are presented here.

It means a lot to know the content feels both entertaining and thoughtful.

I’ve been surfing online greater than three hours these days, but I never discovered any fascinating article like yours. It is beautiful value sufficient for me. In my view, if all webmasters and bloggers made just right content as you did, the web might be much more helpful than ever before.

That’s such a generous and thoughtful message—thank you!

I’m truly honored that the content stood out to you after hours of browsing.

Wonderful website. Lots of useful information here. I’m sending it to several buddies ans additionally sharing in delicious. And naturally, thanks for your effort!

Thank you so much for your kind words and for sharing the site with others!

I’m really glad you found the information helpful.

Greetings! I’ve been reading your site for a while now and finally got the bravery to go ahead and give you a shout out from Dallas Tx! Just wanted to say keep up the excellent work!

Thank you so much for your kind words and warm shout-out from Dallas!

Greetings! Very helpful advice on this article! It is the little changes that make the biggest changes. Thanks a lot for sharing!

Thank you! I’m glad the advice was helpful and I appreciate your kind words.

Hello. excellent job. I did not anticipate this. This is a impressive story. Thanks!

Thank you very much for your kind words. I’m glad you enjoyed the story.

Great post. I am facing a couple of these problems.

Thank you for your honesty! I’m glad the post resonated with you